硬核干货 | Xilinx FPGA 时钟之心:MMCME2_ADV 全面详解

硬核干货 | Xilinx FPGA 时钟之心:MMCME2_ADV 全面详解

FPGA技术江湖

发布于 2026-04-10 14:46:19

发布于 2026-04-10 14:46:19

文 | 资深FPGA架构师

在 FPGA 的浩瀚宇宙中,时钟系统不仅是驱动逻辑运转的“心脏”,更是决定系统稳定性与性能上限的“指挥棒”。对于 Xilinx 7 系列 FPGA 开发者而言,如果仅满足于使用 Clocking Wizard IP 核点点鼠标,往往会在面对复杂的时序收敛、动态频点切换或低抖动需求时束手无策。

今天,我们将剥开 IP 核的外壳,深入到底层原语(Primitive)层面,全方位解析 Xilinx 7 系列中最强大的混合模式时钟管理器——MMCME2_ADV。

一、 为什么你需要关注 MMCME2_ADV?

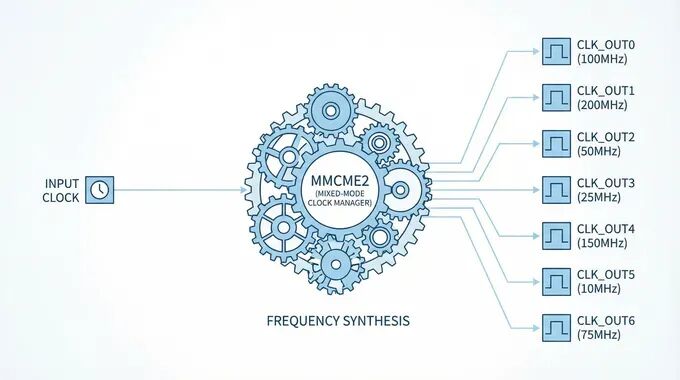

MMCME2_ADV(Mixed-Mode Clock Manager Advanced)是 Xilinx 7 系列 FPGA(Artix-7, Kintex-7, Virtex-7)中最高级的硬核时钟资源。虽然 PLL(锁相环)也能实现分频倍频,但 MMCM 在功能丰富度上具有压倒性优势。

核心能力清单:

- 极致的灵活性:所有输出时钟共享同一个压控振荡器(VCO),但每个通道可独立配置分频、相位和占空比。

- 动态调整能力:支持在系统运行过程中,通过 DRP 接口动态重配置时钟参数,或动态调整相位偏移。

- 信号完整性保障:内置去偏斜(Deskew)电路和抖动滤波器,能显著优化时钟网络质量。

简而言之,它是 FPGA 时钟树设计的核心模块。理解它,是你从“写代码”进阶到“设计系统”的必经之路。

二、 庖丁解牛:核心端口详解

要驾驭这个模块,首先要读懂它的“说明书”——端口列表。MMCME2_ADV 的端口众多,但逻辑清晰。我们将按功能将其分类解析。

1. 时钟输入与控制

端口 | 方向 | 深度解析 |

|---|---|---|

CLKIN1 | 输入 | 主参考时钟输入。绝大多数场景下的主时钟源。 |

CLKIN2 | 输入 | 辅助参考时钟。用于双时钟冗余切换,需配合 CLKINSEL 使用。 |

CLKINSEL | 输入 | 时钟源选择。High=CLKIN1; Low=CLKIN2。支持动态切换。 |

RST | 输入 | 异步复位,高电平有效。输入时钟不稳定时必须复位。 |

PWRDWN | 输入 | 低功耗控制。置 1 时模块休眠,未用时务必接地。 |

2. 时钟输出与反馈

端口 | 深度解析 |

|---|---|

CLKOUT0~6 | 7 路独立输出。CLKOUT4 具备级联能力。 |

CLKOUT0B~3B | 仅前 4 路支持 180° 反相输出,常用于 DDR 接口。 |

LOCKED | 系统设计的生命线。仅当此信号拉高后,下游逻辑才能解除复位。 |

CLKFBOUT | 反馈输出,必须连接到 CLKFBIN。 |

CLKFBIN | 反馈输入,通过反馈回路实现相位的对齐和闭环控制。 |

3. 高级动态控制

- 动态相位偏移:(PSCLK, PSEN, PSINCDEC, PSDONE) 允许在不复位 MMCM 的情况下,微调输出时钟相位。

- 动态重配置 (DRP):(DADDR, DCLK, DEN, DWE, DI, DO, DRDY) 通过类似总线读写的方式,在线修改倍频/分频系数,实现“变频”功能。

三、 核心属性配置:数学与物理的平衡

在例化 MMCME2_ADV 时,参数配置直接决定了时钟的质量。这里涉及两个核心公式:

F_VCO = F_CLKIN × (MULT_F / DIVIDE)

F_OUTx = F_VCO / OUTx_DIVIDE

属性 | 配置指南 |

|---|---|

CLKFBOUT_MULT_F | (2.0~64.0) VCO 的倍频系数。专家提示:务必确保 F_VCO 落在器件手册规定的范围内(通常为 600MHz~1200MHz)。 |

DIVCLK_DIVIDE | (1~106) 输入预分频系数。通常设为 1 以降低抖动,除非输入频率过高。 |

CLKOUTx_DIVIDE | (1~128) 各通道的输出分频系数。 |

BANDWIDTH | OPTIMIZED: 默认推荐。LOW: 滤除输入高频抖动。HIGH: 快速跟踪输入变化。 |

四、 实战代码:VHDL 与 Verilog 例化模板

为了方便各位工程师直接 copy-paste 到工程中,以下提供了标准的例化模板。请根据实际需求修改参数。

1. VHDL 例化模板

-- MMCME2_ADV: 7系列高级混合模式时钟管理器

MMCME2_ADV_inst : MMCME2_ADV

generic map (

BANDWIDTH => "OPTIMIZED",

CLKFBOUT_MULT_F => 5.0, -- VCO设定为输入频率的5倍

CLKFBOUT_PHASE => 0.0,

CLKIN1_PERIOD => 10.0, -- 极其重要!输入时钟周期10ns (100MHz)

CLKOUT0_DIVIDE_F => 5.0, -- 输出分频,最终频率 = 100 * 5 / 5 = 100MHz

CLKOUT0_DUTY_CYCLE => 0.5,

CLKOUT0_PHASE => 0.0,

DIVCLK_DIVIDE => 1,

COMPENSATION => "ZHOLD" -- 零延迟保持模式

)

port map (

CLKOUT0 => CLKOUT0, -- 主时钟输出

LOCKED => LOCKED, -- 锁定信号,连接系统复位

CLKIN1 => CLKIN1, -- 输入参考时钟

RST => RST, -- 复位信号

PWRDWN => '0', -- 始终使能

CLKFBIN => CLKFBOUT, -- 【关键】反馈环路闭合

CLKFBOUT => CLKFBOUT

);2. Verilog 例化模板

// MMCME2_ADV 基础例化

MMCME2_ADV #(

.BANDWIDTH("OPTIMIZED"),

.CLKFBOUT_MULT_F(5.0), // VCO倍频系数

.CLKIN1_PERIOD(10.0), // 输入时钟周期 ns

.CLKOUT0_DIVIDE_F(5.0), // 输出分频系数

.DIVCLK_DIVIDE(1),

.COMPENSATION("ZHOLD")

)

MMCME2_ADV_inst (

.CLKOUT0(CLKOUT0), // 连接至 BUFG

.LOCKED(LOCKED), // 连接至 rst_n 生成逻辑

.CLKIN1(CLKIN1), // 物理管脚输入或上一级时钟

.RST(RST),

.PWRDWN(1'b0),

.CLKFBIN(CLKFBOUT), // 内部反馈

.CLKFBOUT(CLKFBOUT)

);五、 典型应用场景与案例

场景 1:基础时钟倍频(100MHz → 200MHz)

策略:先将 VCO 频率倍频到一个较高的中间值(如 1000MHz),再分频得到 200MHz。较高的 VCO 频率通常能带来更好的抖动性能。

MMCME2_ADV #(

.CLKIN1_PERIOD(10.0), // 输入 100MHz

.CLKFBOUT_MULT_F(10.0), // VCO = 100 * 10 = 1000MHz

.DIVCLK_DIVIDE(1),

.CLKOUT0_DIVIDE_F(5.0) // 输出 = 1000 / 5 = 200MHz

) mmcm_inst ( ... );场景 2:多相位时钟生成(ADC/DDR 采样)

在高速数据采集或 DDR 控制器设计中,常需要 0°、90°、180°、270° 四相时钟。

MMCME2_ADV #(

// ...

// CLK0: 100MHz, 0度

.CLKOUT0_DIVIDE_F(10.0),

.CLKOUT0_PHASE(0.0),

// CLK1: 100MHz, 90度

.CLKOUT1_DIVIDE(10),

.CLKOUT1_PHASE(90.0),

// ...

) mmcm_inst ( ... );场景 3:差分输入与驱动能力

在实际板卡上,时钟源往往是 LVDS 差分信号。此时 MMCME2_ADV 需配合 IBUFDS 使用。同时,MMCM 输出可灵活驱动:

- BUFG:驱动全局逻辑。

- BUFIO:驱动 I/O Bank 内的高速 SerDes。

- BUFR:驱动区域逻辑,降低功耗。

六、 进阶话题:动态重配置(DRP)

MMCME2_ADV 提供了一组标准的 DRP 接口,允许用户读写内部寄存器。原理是通过修改分频计数器(M, D, O)的寄存器值,改变频率合成公式。

注意:修改参数后,必须复位 MMCM 才能使新参数生效。Xilinx 官方提供了 XAPP888 等文档专门讲解如何通过状态机控制 DRP 接口,建议高阶玩家深入研读。

七、 总结与避坑指南

MMCME2_ADV 是 7 系列 FPGA 中功能最全面的时钟管理单元。掌握它,你就掌握了 FPGA 时序设计的“内功”。最后总结几条避坑指南:

- 1. 反馈必须接:CLKFBIN 和 CLKFBOUT 必须连接,否则无法锁定。

- 2. 等待 LOCKED:永远不要使用未锁定的时钟驱动逻辑。

- 3. VCO 范围自检:手动计算 VCO 频率是否在器件手册规定的范围内。

- 4. 复位时机:监测时钟丢失并在恢复后自动复位 MMCM。

*本文基于 Xilinx 7 Series FPGAs Clocking Resources User Guide (UG472) 整理。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-04-07,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录