释放CPO在AI与HPC中的潜力——机遇与挑战并存的光学共封装技术

释放CPO在AI与HPC中的潜力——机遇与挑战并存的光学共封装技术

AI 男神说

发布于 2026-04-02 16:38:01

发布于 2026-04-02 16:38:01

摘要

人工智能和高性能计算的快速发展正在推动数据中心对高带宽、低能耗数据传输的前所未有的需求。传统的可插拔光学模块在功耗、延迟和密度方面面临局限,这促使共封装光学(CPO)作为一种革命性解决方案应运而生。通过将光子器件与ASIC集成,CPO显著降低了功耗并提升了带宽可扩展性。本文全面梳理了CPO技术的最新进展,探讨了设计、制造、热管理和可靠性等关键挑战,并与近封装光学(NPO)进行了对比分析。

引言

随着人工智能(AI)和高性能计算(HPC)等数据密集型应用的快速扩张,数据中心流量呈现出前所未有的增长态势。这些应用需要快速处理和传输海量数据,对现有基础设施提出了极高要求。传统的可插拔式光学模块作为数据中心传统的主力军,正面临越来越难以满足日益增长的带宽密度和能效需求。

共封装光学(CPO)通过将光子器件直接集成到高性能ASIC上,显著降低了功耗并提升了性能,为这一挑战提供了革命性的解决方案。这种集成方式实现了更高效的数据传输,直接响应了AI数据中心日益增长的需求。

什么是共封装光学(CPO)?

可插拔式光模块一直是光学互连的主流选择,但在GPU密集型环境中,它们在带宽、延迟、功耗、物理密度和成本方面的局限性日益显现。此外,信号速度的快速提升也给当前机柜系统中从ASIC到前面板插槽的高速电气走线布线带来了巨大挑战。

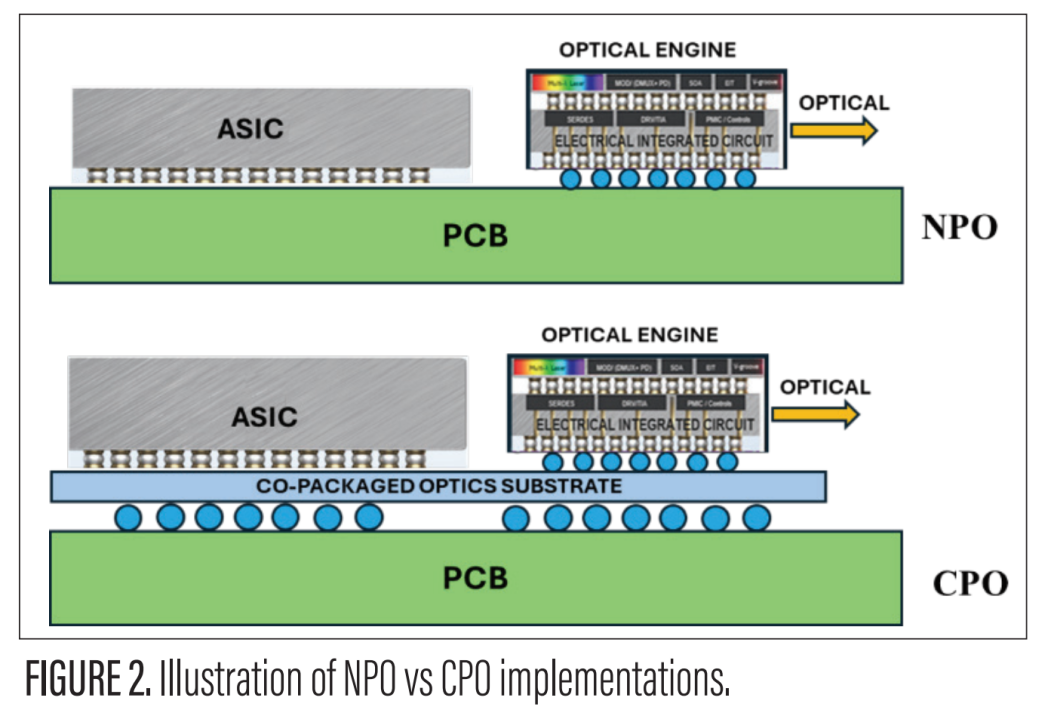

通过将光学器件直接集成到与ASIC相同的基板上,可以显著缩短ASIC芯片与光学I/O之间的电气走线长度。这消除了传统可插拔模块中所需的Retimer和DSP芯片,从而降低功耗并减少延迟。CPO进一步将光学器件直接集成到ASIC封装内,最大限度地减少了信号路径,增强了信号完整性。

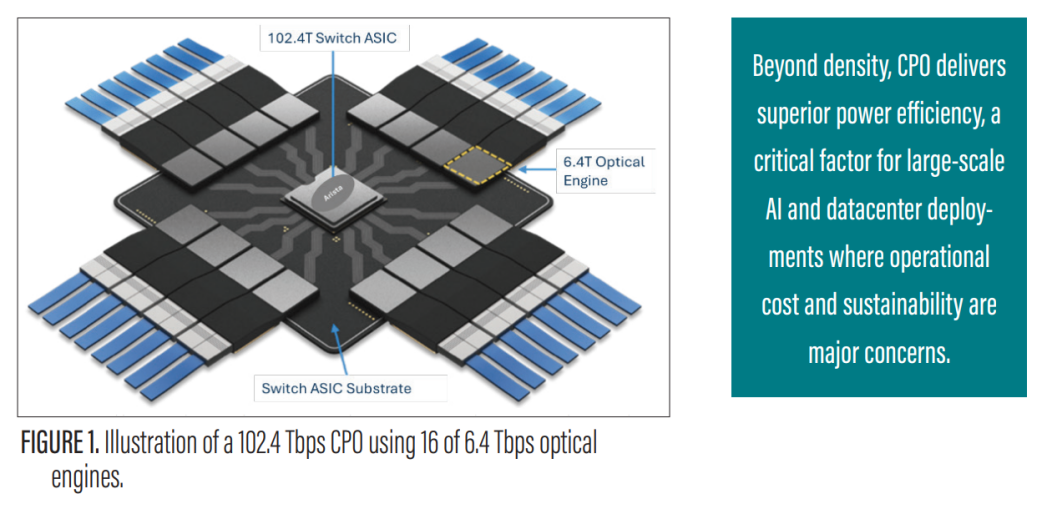

图1:102.4Tbps CPO架构示意图(使用16个6.4Tbps光学引擎)

近年来,多项CPO演示展示了其巨大潜力:2020年,英特尔展示了业界首个基于硅光子学的1.6 Tbps光学引擎,与12.8 Tbps可编程以太网交换机集成。最近,博通展示了一款51.2 Tbps CPO以太网交换机,集成了基于硅光子学的6.4 Tbps光学引擎。

什么是近封装光学(NPO)?

与CPO不同,NPO将光学组件放置在ASIC封装附近,但不在同一基板上。这种配置缩短了电气走线长度,减少了信号插入损耗,并消除了对重时器或DSP的需求,从而改善了延迟和功耗效率。它还简化了与现有系统架构的集成。

图2:NPO与CPO实现方式对比

为支持NPO实现,CEI-112G-XSR+-PAM4实施协议定义了112 Gb/s PAM4电气接口,用于芯片到芯片(D2D)和芯片到光学引擎(D2OE)互连。此外,光学互联网论坛(OIF)还启动了新的CEI-224G项目,旨在建立标准化的电气接口,确保光学与EIC/ASIC之间在224Gbps速率下的兼容性和互操作性。

为什么需要CPO?

随着AI网络扩展到数万个GPU跨多个节点互联,支持大量多太比特每秒互连变得至关重要。CPO凭借其紧凑的集成设计,实现了更高密度的光学连接。

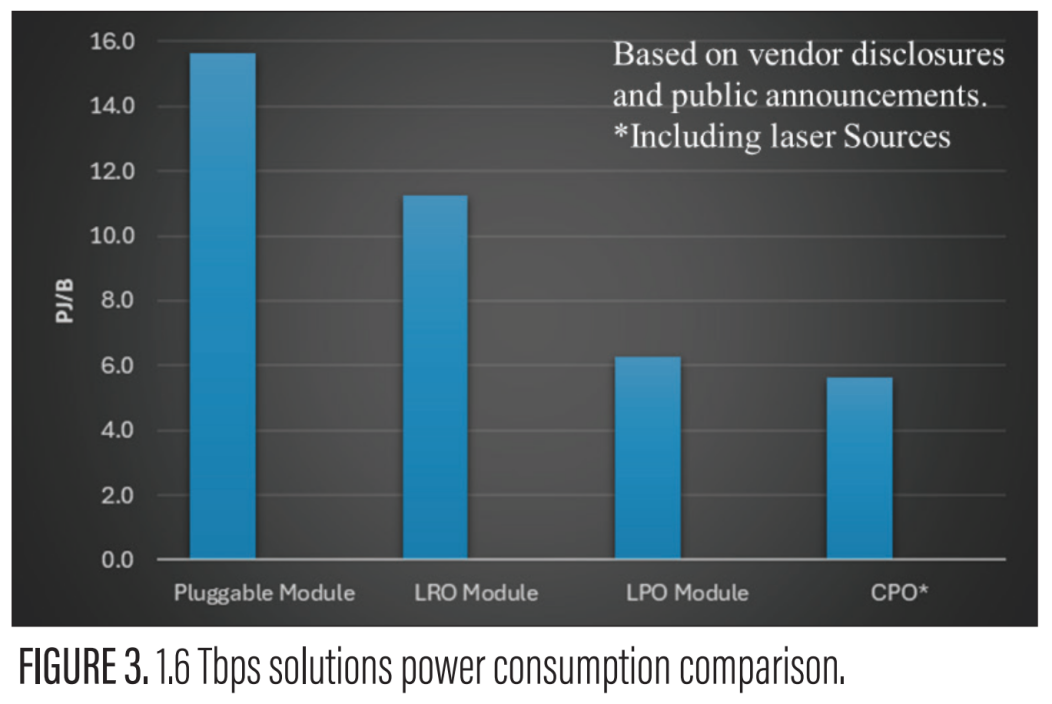

图3:1.6Tbps解决方案功耗对比

例如,一个102.4Tbps CPO模块可以在200×200mm的占位面积内提供512个双向200Gb/s端口,而使用OSFP等可插拔光学实现相同容量则需要64个独立模块,每个约100×23mm。除了密度优势外,CPO还具有卓越的能效。

此外,CPO还提供了显著的成本优势——1.6Tbps可插拔模块通常每Gbps成本约为1美元到0.25美元(取决于传输距离),而CPO可能将这一成本降低到每Gbps约0.10美元。

设计与制造复杂性

CPO制造本质上很有挑战性,特别是由于GPU和网络交换机等ASIC的复杂封装。这些ASIC涉及复杂的基板设计和多个芯片及分立元件的安装。当多个光学引擎安装在同一ASIC基板上时,复杂性显著增加。

这种集成需要先进的封装技术,包括Fan-Out(FO)、2D、2.5D和3D集成,这些技术在结合光子集成电路(PIC)和电子集成电路(EIC)方面发挥关键作用。

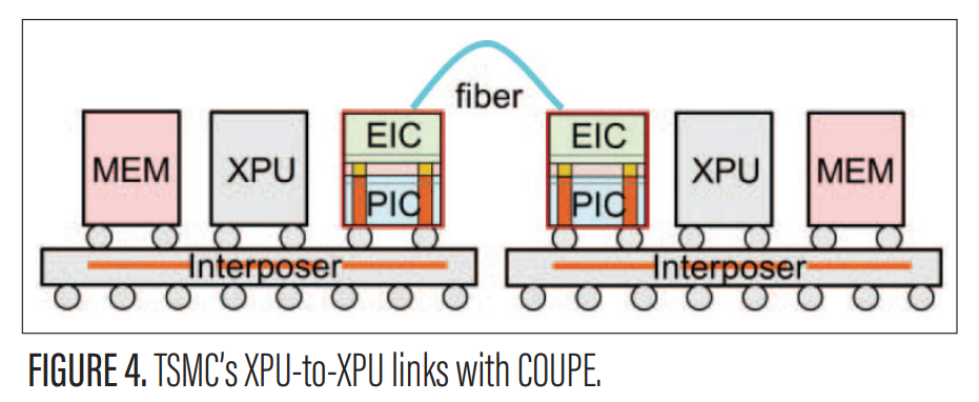

图4:TSMC的XPU-to-XPU互连技术(COUPE)

例如,TSMC的CoWoS(芯片-圆片-基板)和COUPE(紧凑通用光子引擎)技术结合,通过在单一封装内集成EIC和PIC来实现CPO。COUPE结构采用基于SoIC光电集成方案的2.5D/3D封装技术,EIC直接堆叠在PIC之上。

PIC光纤耦合

光纤耦合是CPO设计中的关键元素,它促进了PIC作为独立单元和安装到ASIC基板上时的有效集成和测试。边缘耦合方法通常使用V型槽玻璃块中的光纤阵列与PIC端面对齐。

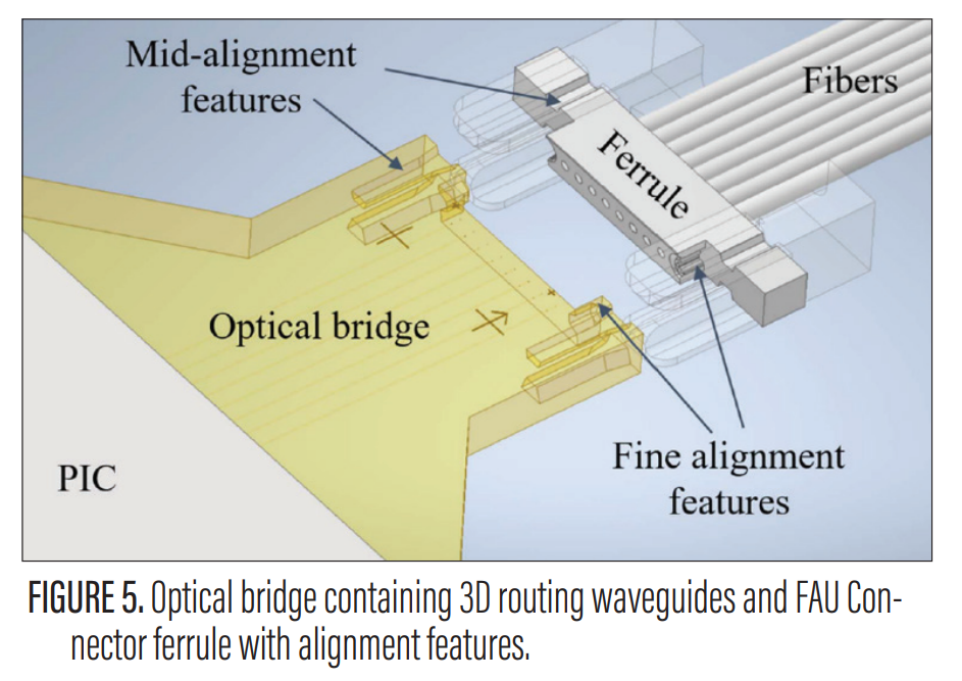

图5:光学桥梁(包含3D导波光波导和FAU连接器)

例如,250μm V型槽可以容纳每毫米4根光纤,而127μm槽可以容纳每毫米8根光纤,提供更高的封装密度。光纤阵列的另一端可以终端连接到各种类型的连接器,如MPO-12、MPO16、MPO32或单独光纤的LC连接器等。

热管理与功耗

将光学器件与GPU和交换机等ASIC集成在同一基板上,由于紧凑区域内的高功耗和热密度,给电源分配和热管理带来了重大挑战。CPO系统在仅200×200mm的基板上总共消耗超过千瓦功率,使高效的电力传输和散热变得至关重要。

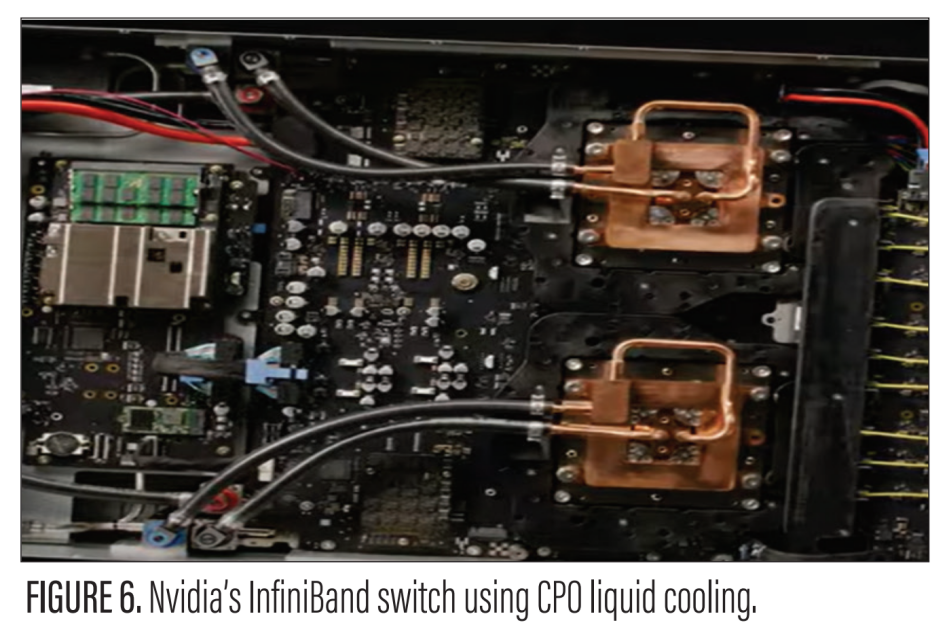

图6:Nvidia InfiniBand交换机使用CPO液冷技术

用于电源分配的铜走线和连接器可能经历高电流密度,在基板内产生大量热量。这需要先进的热管理策略来防止过热,过热可能会对基板、集成组件和特别是对温度高度敏感的光学组件的性能和可靠性产生不利影响。

网络设备中常用的传统强制风冷却通常无法满足CPO的高热密度需求。因此,液冷却已成为必需,目前已在GPU和交换机上使用,提供卓越的散热能力。正在探索各种液冷却方法,包括直接接触封装表面以提取热量的冷板,以及在基板或封装内集成小型流体通道以实现高度局部热控的微通道冷却。

机柜内光纤布线

在传统机柜系统中,光纤连接到插入前面板的可插拔光模块中,光纤被连接器化为LC或MPO以确保稳固性。这些系统内部没有光纤,只有ASIC、电源、控制和监控电路以及用于冷却ASIC的热机械系统。

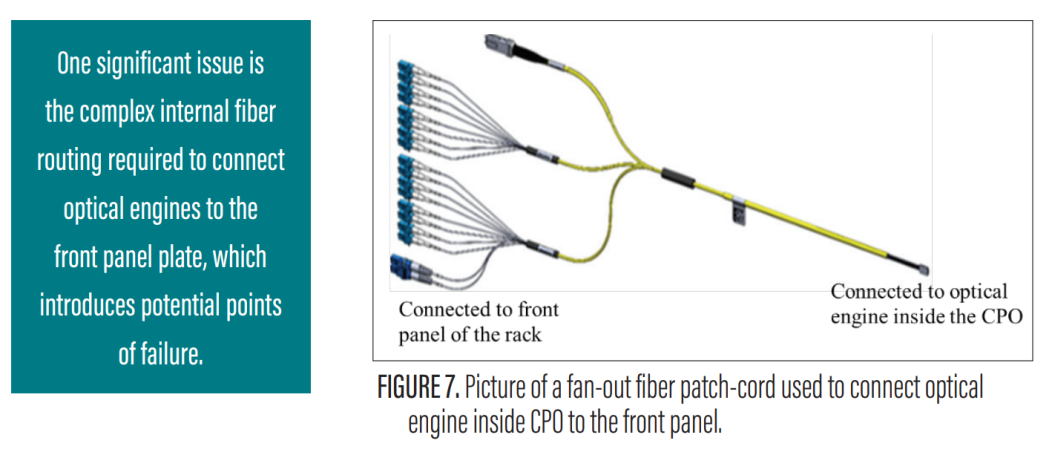

图7:用于连接CPO内部光学引擎到前面板的扇出光纤跳线

相比之下,基于CPO的系统需要将数千根光纤从光学引擎布线到托盘前面板,通过机柜内复杂的章鱼式光纤扇出跳线。对于一个配备16个6.4T光学引擎的102.4T CPO,需要布线16根类似的光纤跳线。

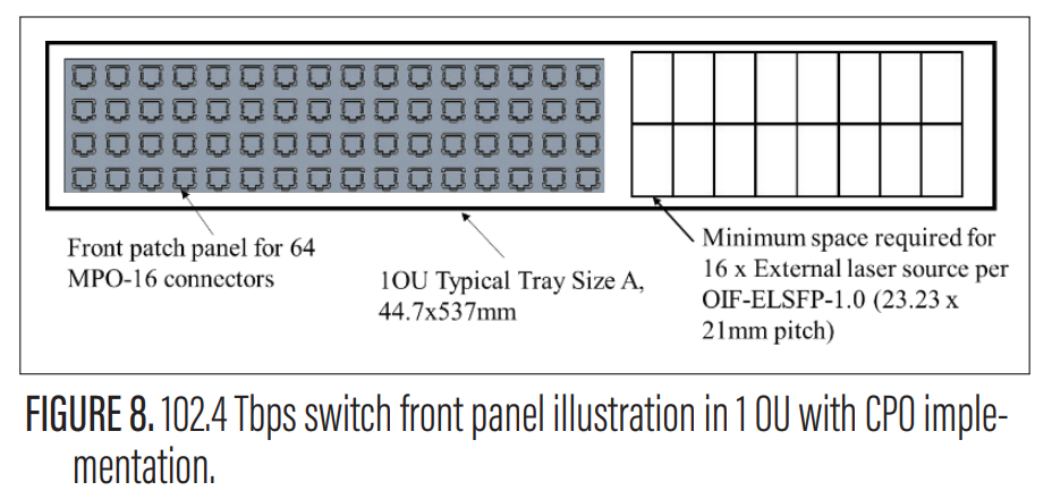

图8:1OU交换机前面板示意图(CPO实现)

假设每个光学引擎需要32根TX光纤(每根200G)、32根RX光纤(每根200G/通道)和8根激光器电源光纤,每根光纤扇出跳线约有72根光纤,因此机柜内总共需要1024根单模光纤用于信号传输和128根偏振保持单模光纤用于激光器电源。

激光光源

CPO系统可以采用异质集成或外部激光光源,每种都有其独特的优势和挑战。集成激光器直接制造在光学调制器上或旁边,提供紧凑的设计、通过消除光纤耦合实现更低的插入损耗,并可能降低成本。

然而,它们由于靠近产热的EIC/ASIC,带来了显著的热管理挑战,以及高质量、多波长或高功率激光器的更高制造复杂性。它们还限制了可维护性,因为集成激光器无法更换或升级。

因此,大多数当前CPO实现倾向于使用外部光源(ELS),通常以QSFP或OSFP模块等标准形式封装。这些紧凑模块通常提供4-8个O波段、CWDM或CW-WDM范围内的连续波(CW)激光器,通常提供超过100mW的光纤耦合光功率。

灵活性、可修复性和可升级性的限制

CPO与可插拔光模块之间的争论仍是光学行业的核心议题。尽管CPO技术在功耗和带宽密度方面提供了显著优势,但其广泛商业采用的潜力和挑战传统可插拔光模块主导地位的能力仍不确定。

实施CPO需要与主要交换机和XPU制造商以及CSP提供商进行深度合作,这可能使这些大公司拥有很大影响力,并可能边缘化较小的公司。与可插拔光模块相比,CPO技术有几个局限性。

它不支持不同类型光学器件的混合匹配,如SR、DR、FR、ZR、AOC和铜缆,这可能限制其通用性。此外,CPO设置无法在同一系统内容纳多种光学技术,如DML、EML、VCSEL和TFLN,进一步限制了灵活性。

标准化与生态系统

标准化工作对于CPO的广泛采用至关重要,可确保互操作性、降低成本并实现生态系统可扩展性。IEEE、光互联论坛(OIF)和开放计算项目(OCP)等关键组织正在推动这一过程。

例如,OIF-Co-Packaging-3.2T-Module-01.0标准针对使用100G PAM4电气通道并向后兼容50G的3.2Tbps以太网交换,支持51.2 Tb/s总带宽交换机。最近,UCIe(通用芯片互联快速)联盟推出了UCIe 3.0,这是一个高速、低功耗的芯片互联标准,每通道支持64Gbps。

CPO可靠性

AI系统极其复杂,具有庞大的计算结构,以Meta的Llama-3-504B为例,该系统使用了16,000个GPU。如此规模的系统中一旦发生故障,就可能导致整个训练过程中断,直到问题解决,从而造成重大的经济损失。价值数亿美元的基础设施即使闲置几分钟,也会导致数百万美元的浪费,并且需要从上一个检查点重新开始,从而丢失自那以来的所有进展。

随着未来的AI系统可能扩展到数十万个GPU以处理更大的推理模型,故障将更加频繁,这个问题预计会进一步恶化。此外,新AI系统的故障率不太可能下降,因为GPU机架变得更加密集、更加耗能、更难冷却,且技术上更加复杂,这可能会增加故障率。

由于ASIC和光学组件在单一封装内的复杂集成,CPO存在几个可靠性问题。一个重要问题是连接光学引擎到前面板所需的复杂内部光纤布线,这引入了潜在的故障点。光纤表面的微观缺陷可能作为应力集中点,导致在不同张力、温度和湿度条件下发生断裂。

此外,集成组件的高功率密度需要有效的热管理来防止过热,过热可能会损害组件的寿命和性能。使用半导体、光纤和环氧树脂等多种材料进一步加剧了可靠性问题,因为这些材料必须在热膨胀、化学稳定性和机械完整性方面相互兼容。这些因素共同增加了缺陷的风险,可能影响整个封装,导致更高的制造成本和复杂性。

在光学方面,激光器退化和故障可能是CPO可靠性的另一个主要问题,但大多数CPO供应商将高功率激光光源置于CPO封装之外,使用可插拔的外部光源(ELS)。这种策略提高了可靠性,并允许轻松更换退化或故障的激光器。

结论

CPO代表了应对下一代AI和HPC数据中心带宽、功耗和密度需求的重大技术飞跃。通过将光子学与ASIC紧密集成,CPO比传统可插拔光学具有更优越的能效、更低的延迟和更高的带宽密度。

然而,封装复杂性、热管理、光纤布线和生态系统标准化等方面的挑战继续阻碍大规模部署。行业协作努力、先进制造技术和标准化接口将是释放CPO全部潜力的关键。最终,CPO将在实现未来可扩展、高效和高性能数据中心架构方面发挥革命性作用。

END

备注:本文翻译自Arista Networks的最新论文《Unlocking the Potential of Co-Packaged Optics in AI and HPC: Opportunities and Challenges》,paper原文放到知识星球了,还有更多AI光互连业界动态和报告更新,欢迎下载学习~

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-28,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录