CXL+XL-FLASH:高性能内存替代方案

CXL+XL-FLASH:高性能内存替代方案

数据存储前沿技术

发布于 2026-04-15 15:42:21

发布于 2026-04-15 15:42:21

阅读收获

- 理解XL-FLASH 16 Planes与MLC模式如何平衡高IOPS、低延迟与成本,指导AI训练中热数据层选型。

- 掌握CXL内存扩展在Redis/Memcached下的实战:25%卸载仅5%损耗,利用Prefetch与TPP实现零感知替换DRAM。

- 对比KIOXIA高性能SCM vs. Solidigm QLC CSAL,评估混合负载(如ScyllaDB+SPEC CPU)下TCO优化路径,提升行业分析准确性。

- 洞察Hotness Monitoring Unit(HMU)补丁,推动内核从被动调度向硬件感知演进,助力RAG/图计算场景落地。

全文概览

在AI与大数据时代,内存墙与存储I/O瓶颈已成为数据中心痛点:DRAM成本高企、容量有限,传统SSD延迟过高,无法满足大模型Checkpointing与RAG向量搜索的需求。KIOXIA的XL-FLASH第二代方案应运而生,作为SCM介质,其读取延迟降至5-10μs,16 Planes高并行设计填补DRAM(纳秒级)与NAND(百微秒级)间的性能鸿沟。通过CXL协议,XL-FLASH实现内存语义访问,模糊内存-存储边界,支持512GB单卡扩展(2026 Q2商用)。

你是否好奇:在30μs延迟下,Redis性能仅降5%,如何用廉价闪存替换33% DRAM却维持98.4%系统效能?FPGA仿真验证了Linux TPP与Prefetch机制的有效性,CacheLib异步架构进一步掩盖延迟。这不仅是硬件创新,更是构建HBM→DRAM→CXL的三级内存金字塔,推动TCO优化。KIOXIA高性能路径,与Solidigm QLC密度策略形成鲜明对比,揭示厂商对异构负载的精准洞察。

👉 划线高亮 观点批注

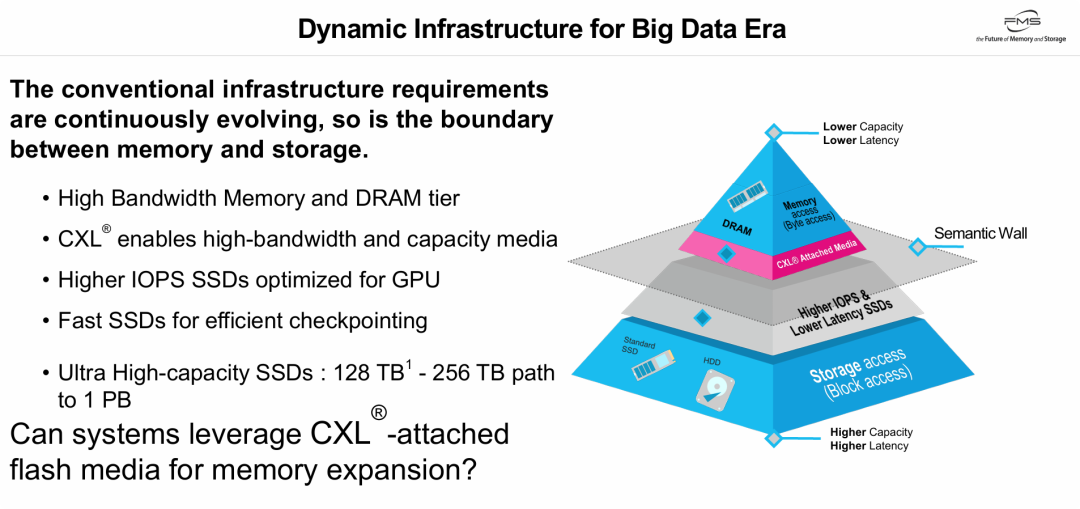

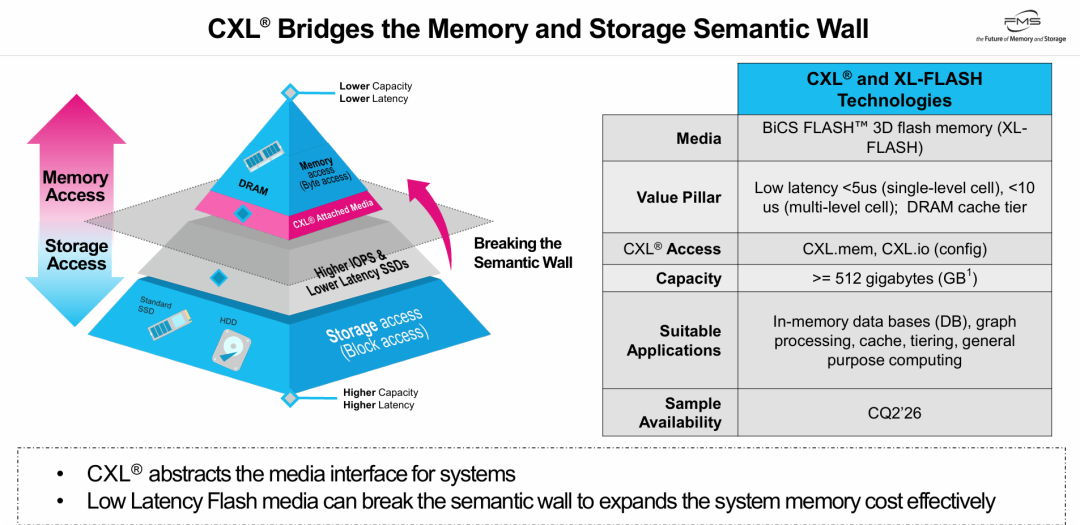

图片展示了在 AI 与大数据驱动下,内存(Memory)与存储(Storage)层级结构的演进,重点探讨了 CXL (Compute Express Link) 在弥合两者鸿沟中的作用。

- 内存与存储边界的模糊化(Convergence): 随着 CXL 技术的引入,传统的“内存 vs. 存储”二元划分正在被打破。CXL 挂载介质(CXL Attached Media)正在通过突破“语义壁垒”,使非易失性介质能够以接近内存的语义进行访问,填补了 DRAM 与 SSD 之间的性能与成本缺口。

- 存储容量的指数级飞跃: 针对大数据应用,存储单盘容量正在经历巨大跨越。从目前的 128TB 级别,向 256TB 乃至 1PB(1024TB) 的超大容量 SSD 演进,反映出数据中心对极致存储密度的迫切需求。

- 异构计算驱动的针对性优化: 现代基础架构不再是通用的,而是针对特定负载进行分层优化。例如,专门为 GPU 提供的高 IOPS SSD,以及利用 CXL 扩展内存池(Memory Expansion),都是为了解决 AI 训练中频繁的 Checkpointing 和大模型参数存储带来的 I/O 瓶颈。

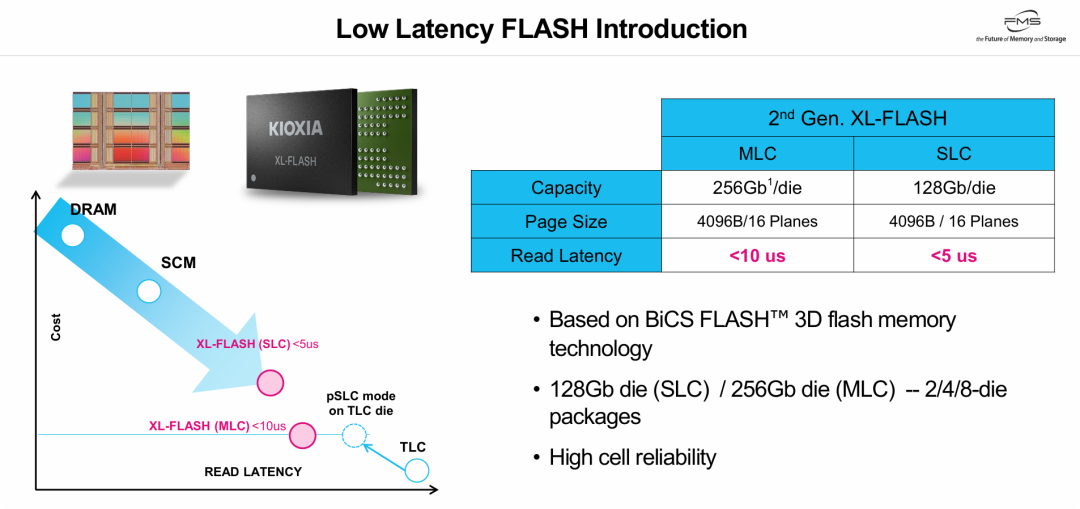

图片通过性能曲线对比和技术参数表,详细介绍了第二代 XL-FLASH 的定位与规格。

- 填补 DRAM 与 NAND 之间的“性能鸿沟”: XL-FLASH 的核心价值在于其 SCM(存储类内存) 的定位。通过将读取延迟降低至 5μs - 10μs 级别,它填补了 DRAM(纳秒级)与传统 SSD(百微秒级)之间的巨大断层,是构建热数据加速层的理想介质。

- 通过高并行架构提升吞吐: 规格表中提到的 16 Planes 设计是一个关键技术点。相比传统闪存通常的 2 或者 4 Planes,16 Planes 显著提升了芯片内部的并行操作能力,在降低延迟的同时大幅增强了带宽表现。

- 多层级策略平衡成本与性能: 第二代 XL-FLASH 引入了 MLC 模式。这表明该技术正在寻求性能与经济性的平衡点——既能提供远超普通 SSD 的响应速度,又能通过更高的存储密度(256Gb)降低单位成本,从而更适合大规模部署。

与Solidigm、三星等一众押注QLC 大容量SSD存储器厂商相比,KIOXIA 似乎在高性能场景情有独钟

Cite

维度 | Solidigm (QLC 方案) | KIOXIA (高性能方案) |

|---|---|---|

技术核心 | CSAL (云存储加速层) 软件优化 | XL-FLASH (SCM 介质) 硬件创新 |

解决思路 | 用 SLC 盘做缓存,通过软件将随机写转为顺序写,保护 QLC 寿命。 | 开发介质层面的“怪兽”,通过增加 Plane 数量(如 16 planes)提升并行度。 |

优势 | 密度极高。单位机架能支撑的存储量惊人,电力效率极佳。 | 响应极快。几乎消除了 I/O 等待,适合高频交易、实时 AI。 |

局限 | 随机写入是硬伤,必须依赖复杂的软件栈(如 SPDK/CSAL)。 | 成本昂贵,容量通常较小(如 800GB - 3.2TB 级别)。 |

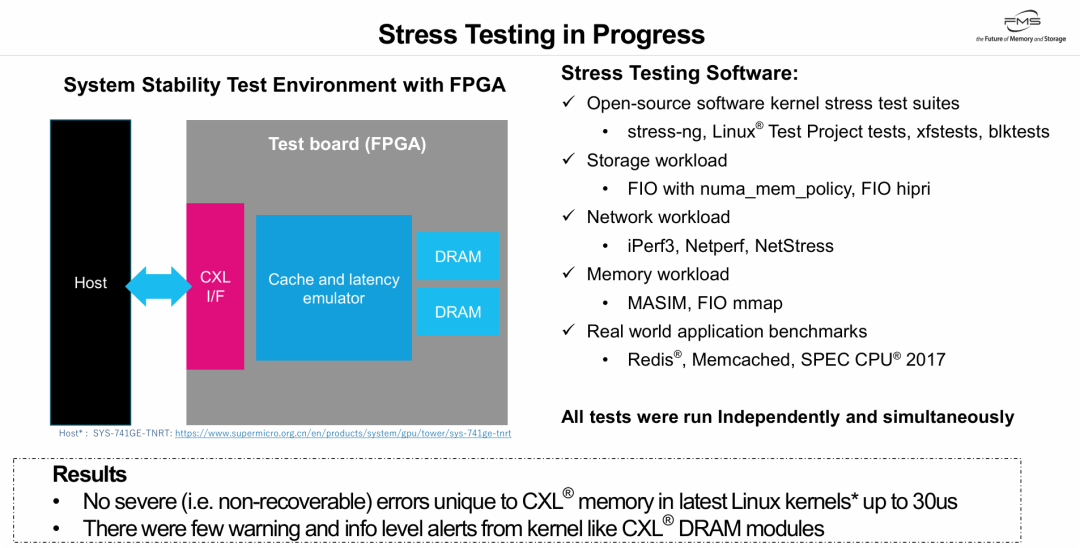

图片详细记录了基于 FPGA 的 CXL 仿真测试环境及其测试结果。

- 验证 CXL 内存的“高延迟容忍度”: 这是一个非常重要的信号。测试在 30μs 延迟下运行(这远高于原生 DRAM 的百纳秒级,属于 CXL 闪存或 SCM 的延迟区间)。结果显示内核能够稳定运行,证明了 Linux 系统对“慢速内存”作为 CXL 扩展槽的初步兼容性已经成熟。

- 软硬件解耦的仿真策略: KIOXIA 利用 FPGA 模拟器来预研 CXL。这种方式不仅能验证硬件逻辑,更重要的是测试 软件栈(Software Stack)。提到的

numa_mem_policy表明测试重点在于多 NUMA 节点下的内存分配策略,这是 CXL 落地最难的软件适配环节。 - 从基准测试走向真实应用: 测试名单中出现了

Redis和Memcached。这表明 KIOXIA 认为 CXL 内存的最佳首发场景是内存数据库和分布式缓存。这些应用对容量极其敏感,且能够容忍微秒级的延迟增加,是 CXL 商业化的“甜点位”。

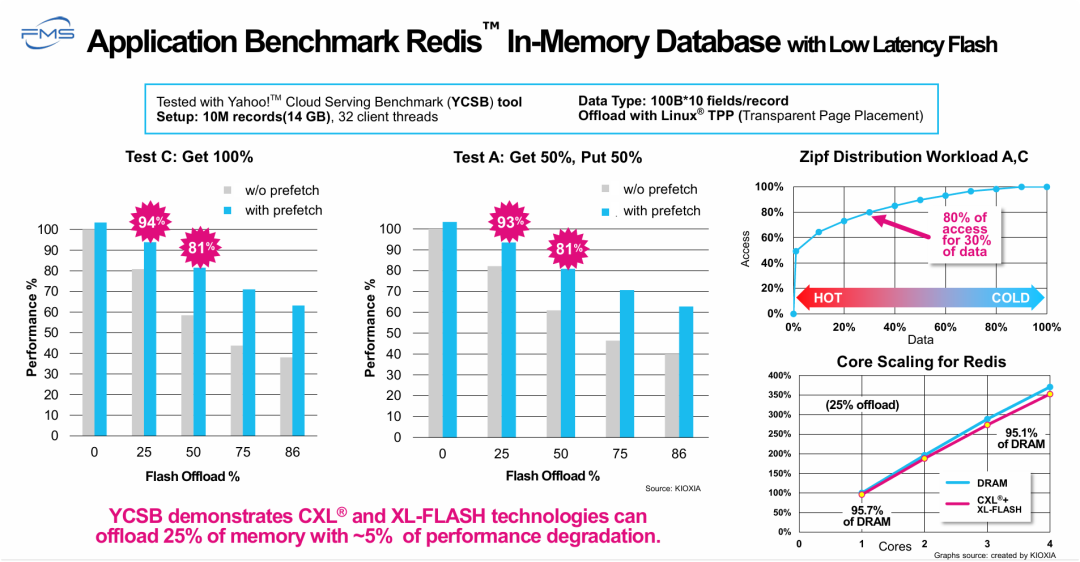

图表展示了利用低延迟闪存(XL-FLASH)配合 Linux TPP (Transparent Page Placement,透明页面放置) 机制,在 Redis 数据库上进行内存卸载(Offload)的性能表现。

- “25% 规则”下的极低损耗: 图片底部的红字给出了最核心的结论:将 25% 的内存负担交给 CXL 和 XL-FLASH,仅会带来约 5% 的性能下降。 这对于数据中心运营商来说极具吸引力,因为可以用更廉价的闪存替代昂贵的 DRAM,而用户几乎感知不到速度差异。

- Prefetch(预取)是性能救星: 图中蓝色柱状图(with prefetch)明显高于灰色柱状图(w/o prefetch)。这说明在处理微秒级延迟的介质时,通过软件算法提前预判并加载数据,可以有效弥补 XL-FLASH 与 DRAM 之间的速度鸿沟。

- TCO(总拥有成本)的降维打击: 结合右侧的扩展性图表,该方案证明了在不牺牲系统扩展能力的前提下,利用 CXL 技术可以实现大规模、低成本的内存容量扩展。这对于动辄需要 TB 级内存的生成式 AI 推理或大规模缓存系统来说,是极佳的商业路径。

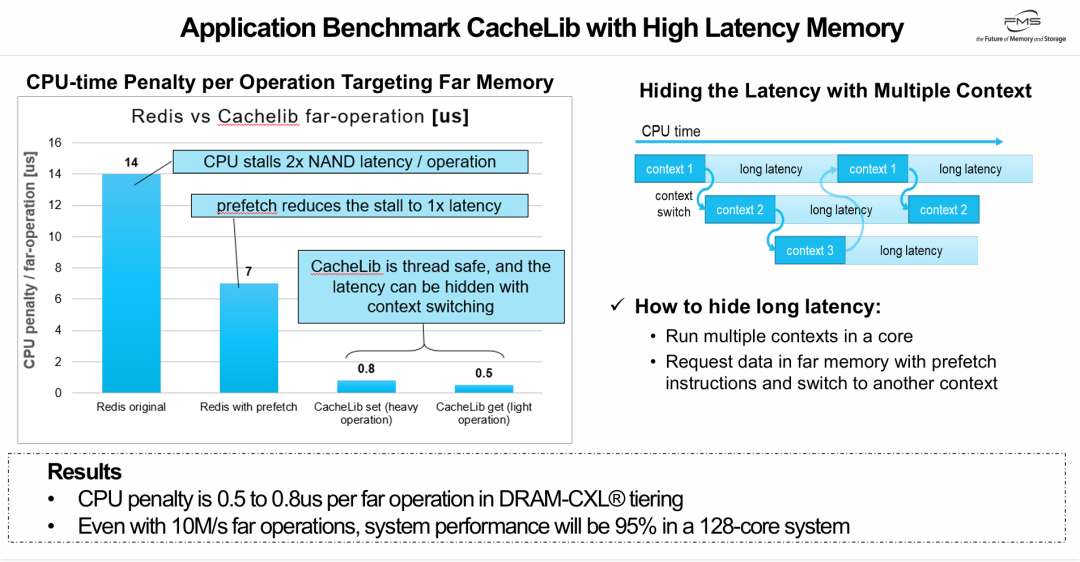

图通过对比 Redis 与 CacheLib(Meta 开源的分布式缓存库)在处理“远端操作(Far-operation)”时的 CPU 开销,展示了延迟掩盖技术。

- “软件定义存储”向“软件适配内存”演进: 传统的 Redis 在设计时假设内存延迟是恒定的(纳秒级),因此在遇到 CXL 的微秒级延迟时会产生巨大的 CPU 停顿。而像 CacheLib 这种现代异步架构,天然具备线程安全和高并发处理能力,更适合 CXL 环境。

- 异步化与并行化是 CXL 落地的金钥匙: 核心观点是 “延迟不可避免,但可以被隐藏”。通过增加系统的并发深度,利用 CPU 上下文切换来填充等待 CXL 数据的空窗期,将原本高达 14μs 的物理延迟,在 CPU 效率层面“稀释”到了不足 1μs。

- 128 核时代的系统红利: 随着服务器核心数激增(如 128 核),系统有足够的计算资源来通过频繁切换掩盖延迟。这意味着在现代高性能服务器中,引入 CXL 扩展内存的边际性能损失已经低到可以忽略不计。

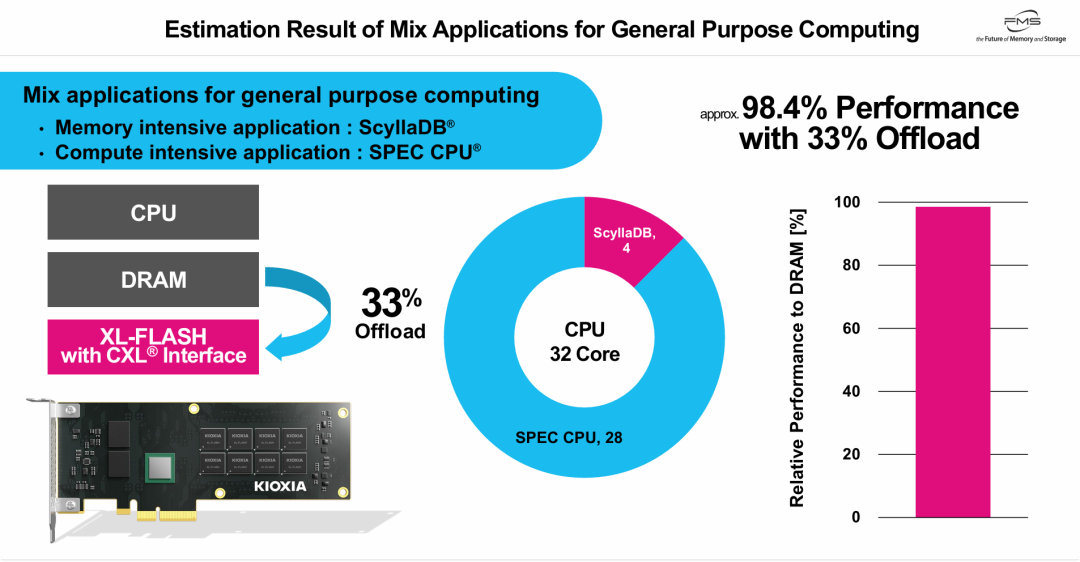

展示了在混合运行内存密集型和计算密集型任务时,系统性能的预估结果。

- 通用计算场景下的“零感知”扩展: 此前讨论的都是单一 Redis 测试,而本图证明了在混合负载下,即使卸载比例提高到 33%(三分之一内存),性能依然能维持在 98.4%。这标志着 CXL 扩展内存已经完全具备了进入通用服务器市场的成熟度。

- 异构负载的互补效应: 计算密集型任务(SPEC CPU)通常对延迟不敏感但占用大量核心,而内存密集型任务(ScyllaDB)对带宽和延迟敏感。KIOXIA 通过合理的资源调度,证明了在真实的多任务环境中,CXL 带来的微小延迟可以被其他不依赖内存 I/O 的任务所“稀释”。

- CXL 方案的商业化闭环: 左下角的实物卡图片表明,这不再只是实验室的 FPGA 模拟,而是已经具备物理形态的准商用产品。通过 “33% 内存卸载 = 98.4% 性能维持” 这个公式,KIOXIA 成功为数据中心客户勾勒出了一个大幅降低内存采购成本、同时保持系统性能基本不变的完美商业模型。

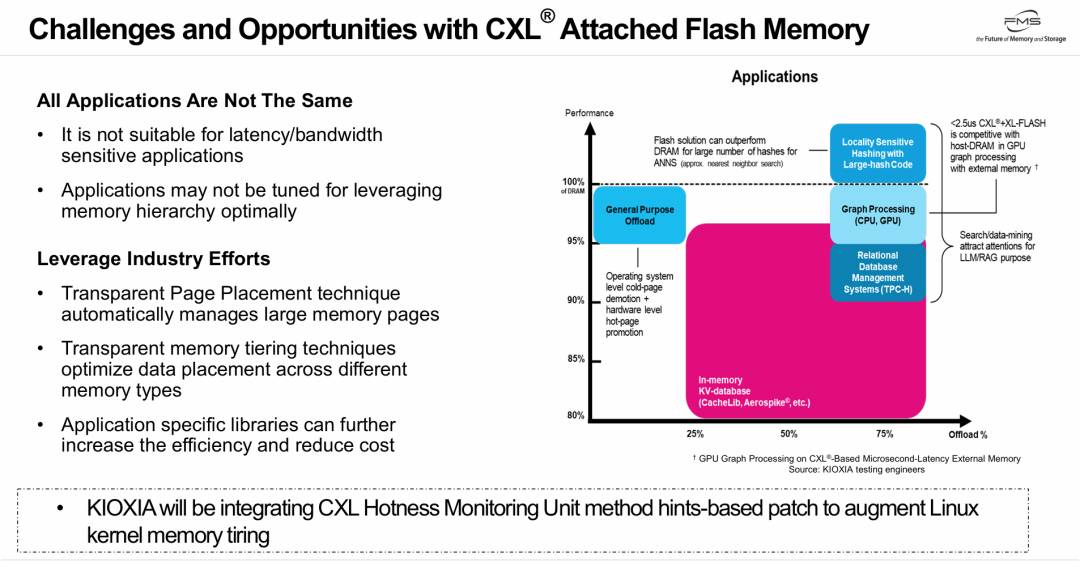

图片通过左侧的理论分析和右侧的性能矩阵,构建了一个完整的技术实施和选型框架

- AI 检索与 RAG 是“天选场景”: 图片右侧标注了 “LLM/RAG” 目的。对于大语言模型检索增强生成(RAG)所需的向量搜索(ANNS)和大规模数据挖掘,CXL 闪存不仅能提供 PB 级的近端存储,还能在特定哈希算法下提供优于传统架构的性价比。

- 从“透明分层”向“智能硬件感知”演进: 底部提到的 Hotness Monitoring Unit (HMU) 补丁是一个重大技术动向。这意味着 KIOXIA 正在推动硬件(CXL 控制器)直接向操作系统内核提供“数据热度”线索,从而让 Linux 的内存调度从“被动猜测”变为“主动预知”,这是进一步抹平延迟的关键。

- 非线性的性能/成本收益: 矩阵显示,并非所有应用在增加卸载比例时都会性能骤降。图计算(Graph Processing)和关系型数据库(TPC-H)在 CXL 上的表现异常坚挺。这意味着对于这些特定负载,用户可以大胆地将 75% 甚至更多 的内存预算替换为 CXL 闪存,实现极致的 TCO 节省。

- “协议即生产力”: CXL 最大的贡献不在于速度,而在于抽象化。它让主机系统不再关心后面挂的是 DRAM 还是 XL-FLASH。通过 CXL.mem 协议,闪存跨越了“语义壁垒”,从慢速的 I/O 设备跃升为 CPU 可以直接寻址的内存资源。

- 大容量内存的“平替”时代开启: 右侧表格中的 512GB 容量与 2026 年 Q2 的时间节点非常关键。这预示着一年后,数据中心将迎来一场硬件变革:用单卡 512GB 的 CXL 闪存来部分替代昂贵的内存条,从而以极低的成本解决 AI 模型参数膨胀带来的内存容量焦虑。

- 构建三级内存金字塔: 结合整套 PPT,KIOXIA 实际上在推行 HBM -> DRAM -> CXL (XL-FLASH) 的新型内存分层体系。XL-FLASH 不再试图取代 SSD,而是要在 DRAM 的成本无法支撑、而普通 SSD 的延迟又太高时,成为那个“性价比最优解”。

延伸思考

这次分享的内容就到这里了,或许以下几个问题,能够启发你更多的思考,欢迎留言,说说你的想法~

- 在PB级RAG应用中,CXL XL-FLASH的微秒延迟如何与GPU异构计算深度整合,潜在瓶颈何在?

- KIOXIA高性能路径与QLC大容量策略,谁更适合未来数据中心的多租户混合负载?

- Linux软件栈需哪些关键适配(如numa_mem_policy扩展),才能让CXL闪存真正进入通用服务器市场?

原文标题:Memory Expansion with CXL® Interface with Low-latency Flash[1]

Notice:Human's prompt, Datasets by Gemini-3-Pro

#FMS25 #CXL内存扩展

---【本文完】---

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-04-05,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读