OFC 2026论坛核心洞察:TFLN商用在即,产业机遇与落地挑战全维度梳理(Hyperlight/Ciena/Broadcom/Eoptolink/Jabil)

OFC 2026论坛核心洞察:TFLN商用在即,产业机遇与落地挑战全维度梳理(Hyperlight/Ciena/Broadcom/Eoptolink/Jabil)

光芯

发布于 2026-04-03 08:49:01

发布于 2026-04-03 08:49:01

◆ HyperLight:TFLN规模化商用的核心技术与量产底座

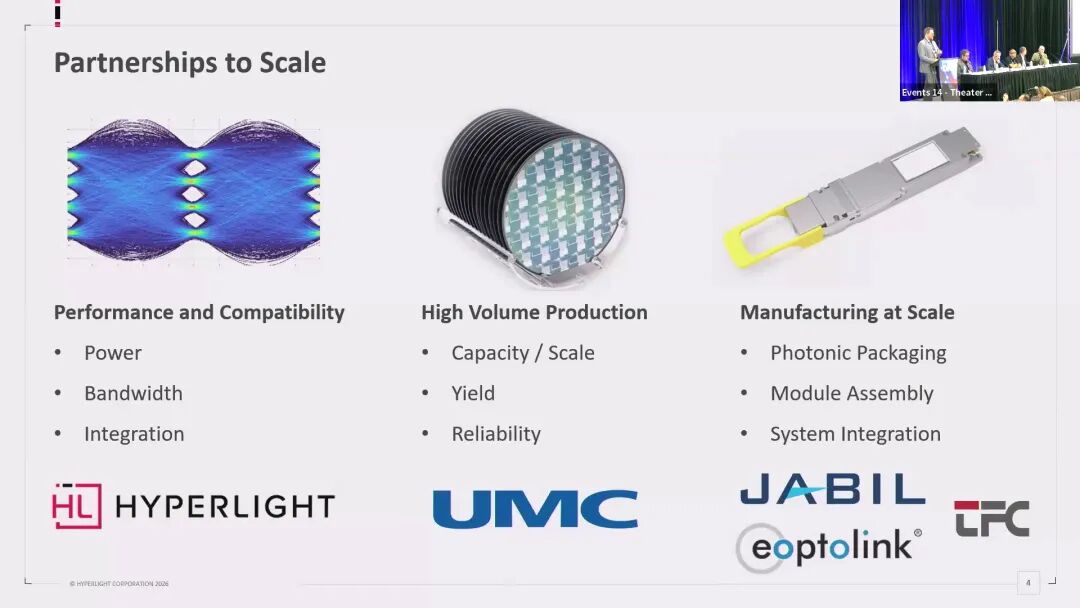

HyperLight源自哈佛大学Marko Loncar团队十余年的TFLN核心技术研发,2018年正式成立,是本次论坛产业链落地的核心器件供应商,Eoptolink、Jabil的相关产品均基于其TFLN芯片开发,并配套Broadcom DSP完成系统级验证。

① 核心技术突破与积淀

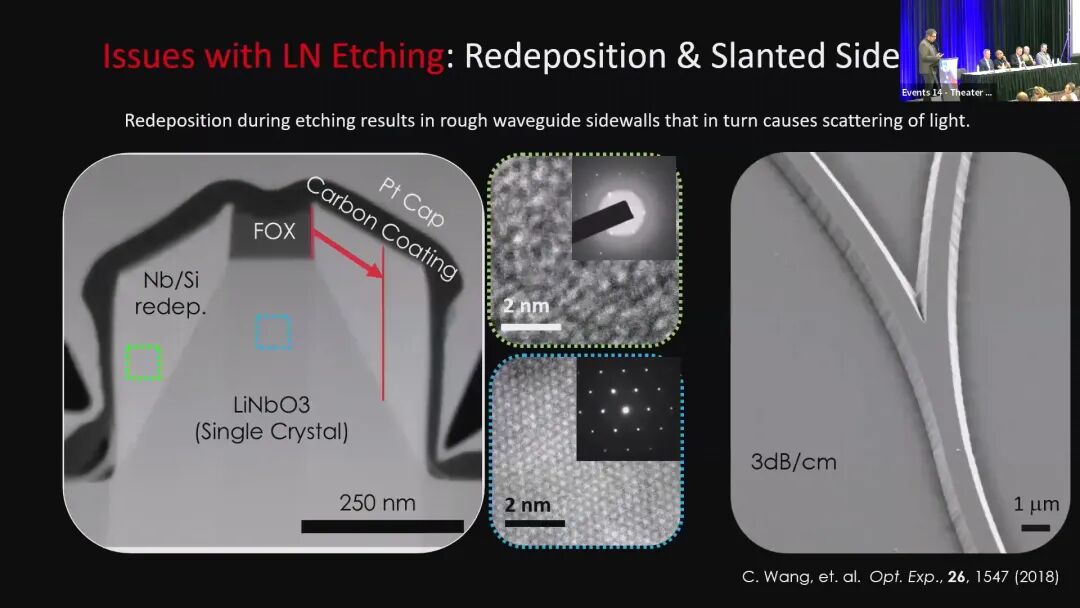

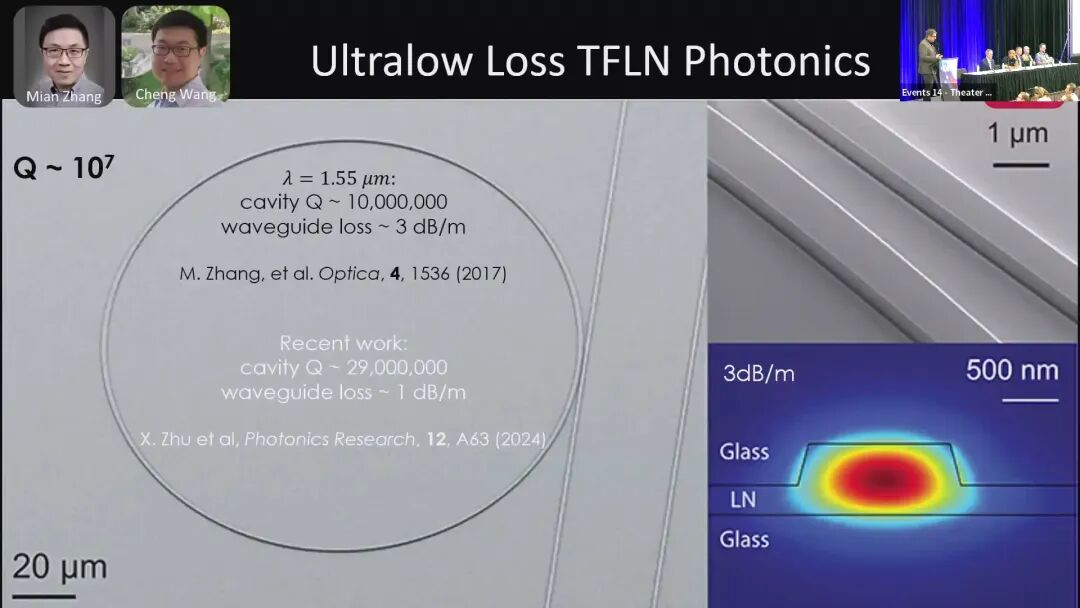

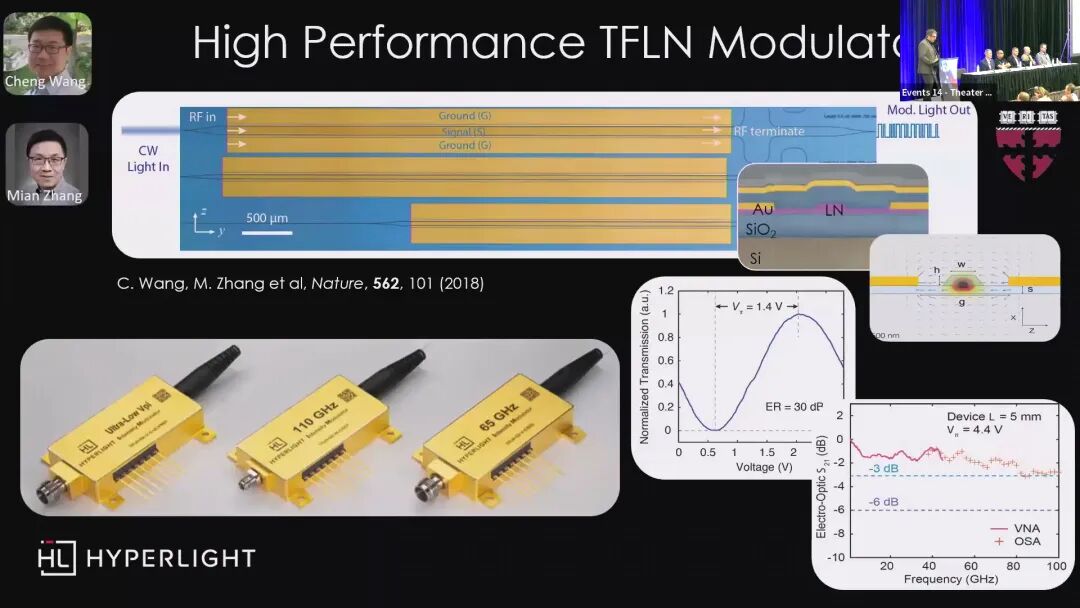

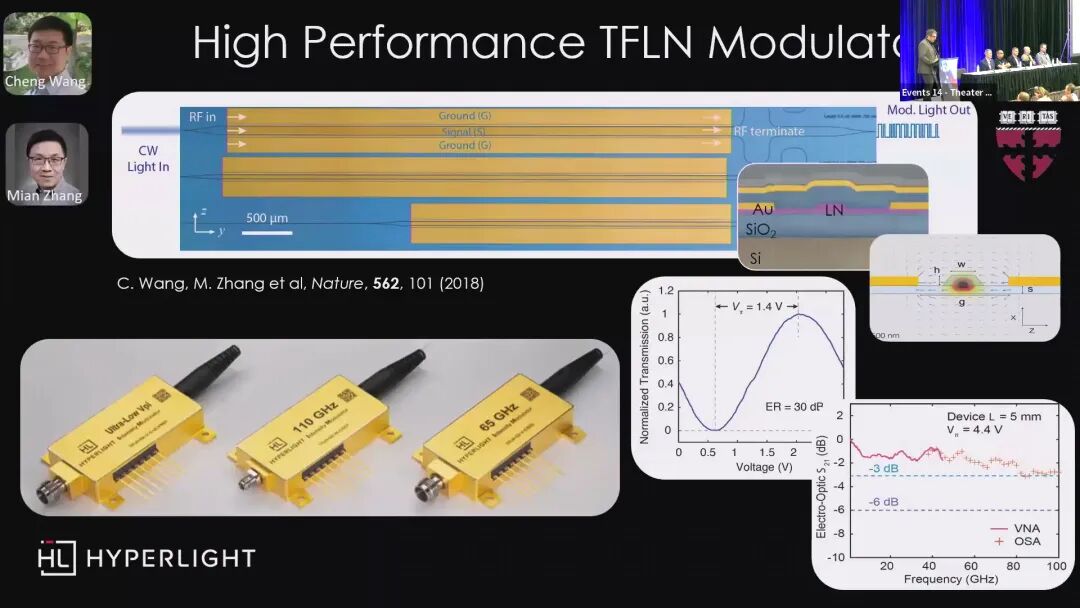

HyperLight团队解决了TFLN产业化的核心工艺瓶颈——刻蚀过程中的材料再沉积与波导侧壁倾斜问题,实现了超低损耗光波导的可控制造。其技术演进从早期3dB/cm的波导损耗,优化至实验室1dB/m的行业领先水平,理论材料损耗极限可达0.1dB/m;同时实现了超高速、低半波电压(Vpi)的电光调制器核心技术,支撑了110GHz以上的调制带宽与<2V的低驱动电压,相关成果发表于《Nature》《Nature Photonics》等顶刊,累计拥有200+技术论文、30+授权专利与40+在审专利。

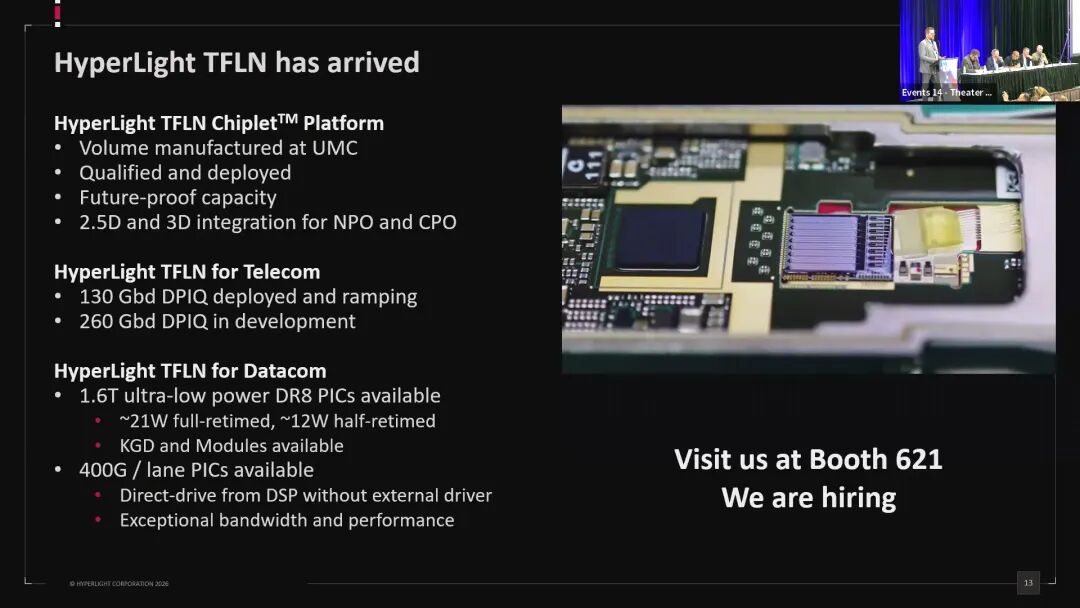

② 量产能力与供应链建设

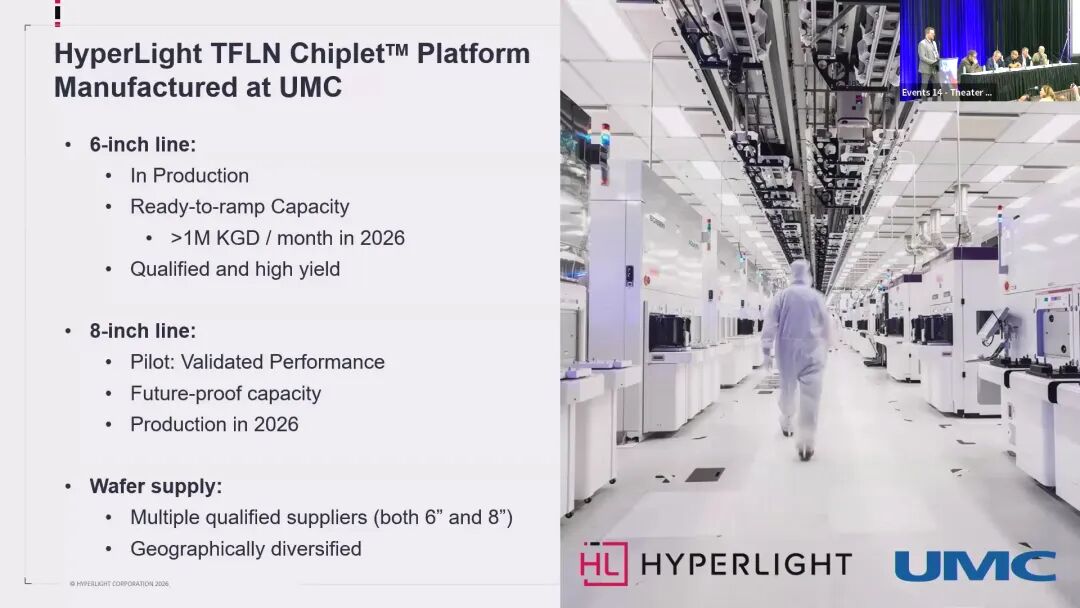

HyperLight与全球头部CMOS晶圆厂UMC深度合作,完成了TFLN芯片的CMOS式规模化量产落地:

- 6英寸产线已正式量产,具备成熟的高良率工艺,2026年可实现每月超100万颗已知合格芯片(KGD)的产能爬坡能力;

- 8英寸产线已完成性能验证,进入试点阶段,2026年内将正式投产,为未来产能扩容提供充足保障;

- 晶圆供应端已搭建多元化、地理分散的供应链体系,拥有多家6英寸、8英寸晶圆合格供应商,消除供应链单点故障风险。

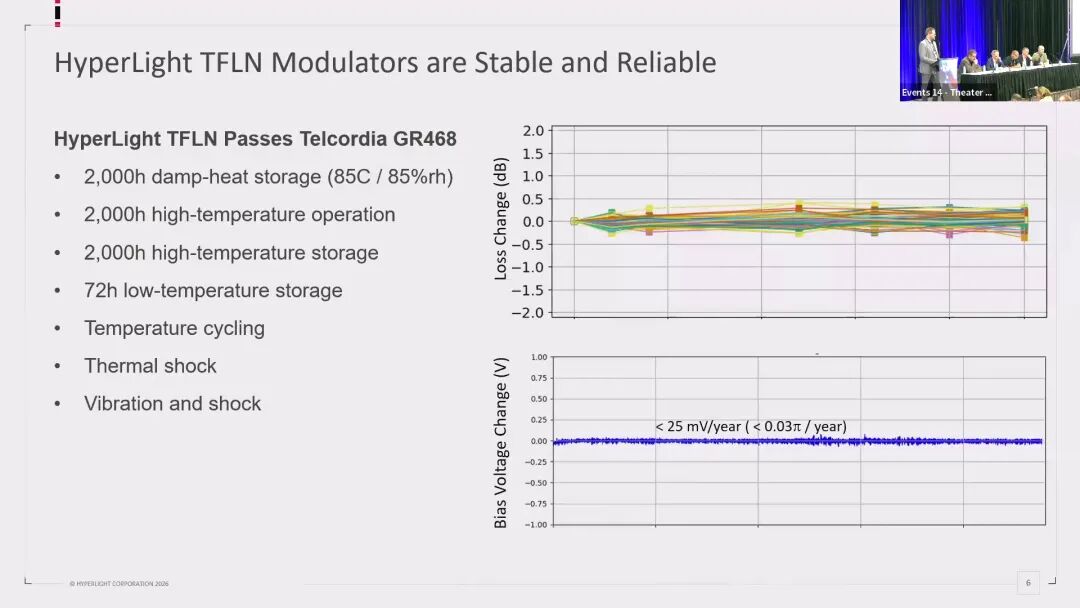

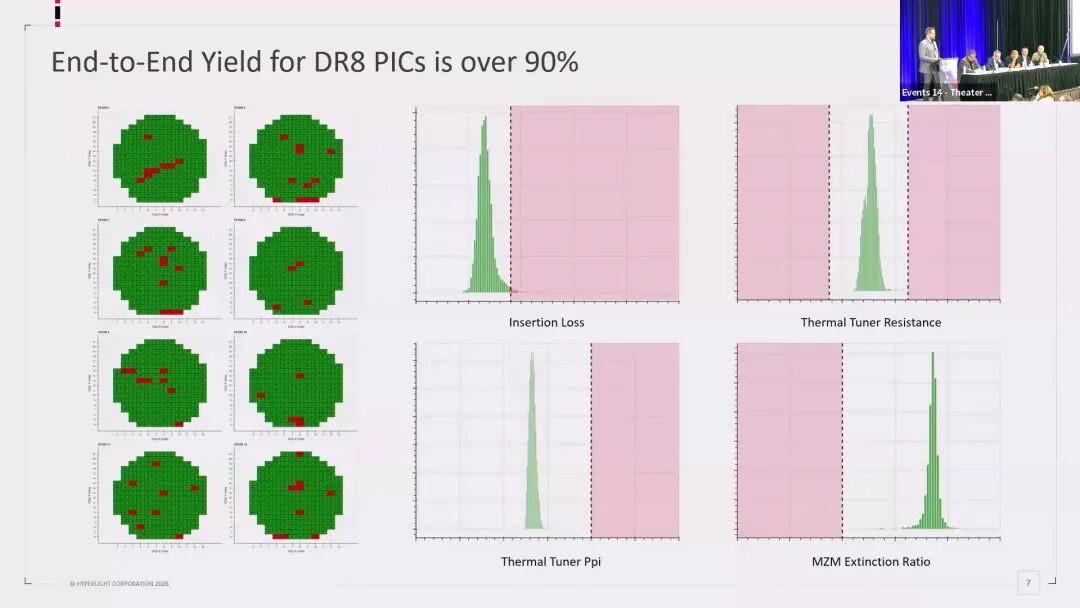

③ 可靠性与良率验证

HyperLight TFLN芯片已通过Telcordia GR468全套电信级可靠性认证,覆盖2000小时85℃/85%RH湿热存储、2000小时高温工作、2000小时高温存储、低温存储、温度循环、热冲击、振动冲击等全项测试,器件偏置电压年漂移量小于25mV,年变化率低于0.03%。同时,其数通DR8光子集成芯片(PIC)实现了超90%的端到端良率,达到规模化量产的良率要求。

③产品矩阵与商用落地

HyperLight已形成覆盖电信、数通全场景的TFLN产品矩阵,核心产品均已完成验证或规模部署:

1. 电信领域:130Gbaud TFLN DPIQ PIC已通过GR468认证、模块与系统级验证,目前正在规模部署与上量;260Gbaud TFLN DPIQ PIC分为绑线版本(Alpha阶段)与flip chip版本(预Alpha阶段),覆盖O波段、C/L波段,支持差分驱动,兼容集电极开路驱动器,芯片尺寸仅4×10mm,适配下一代超高速相干传输需求。

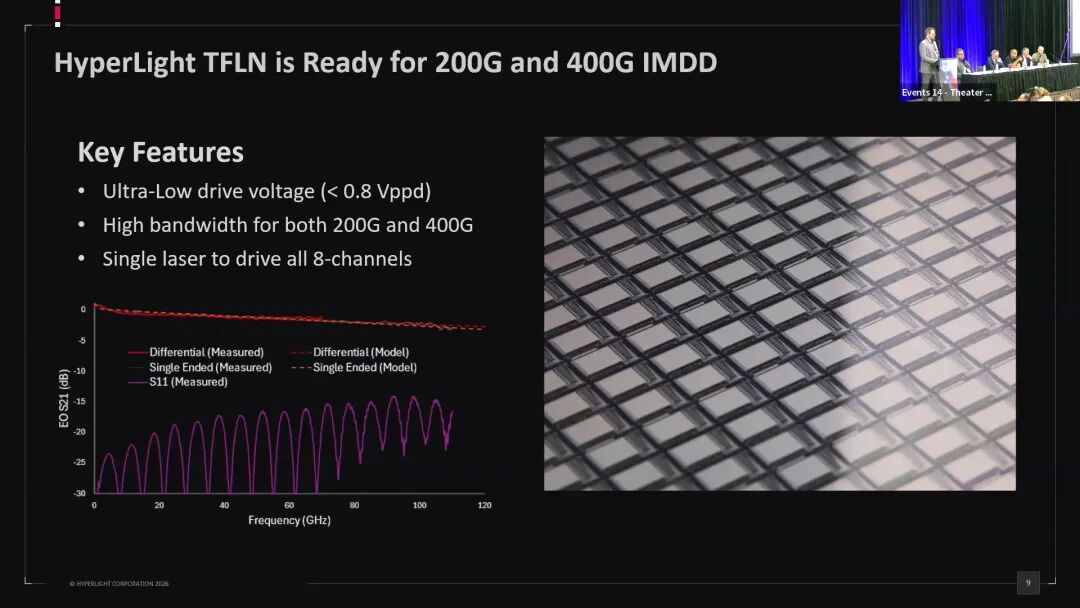

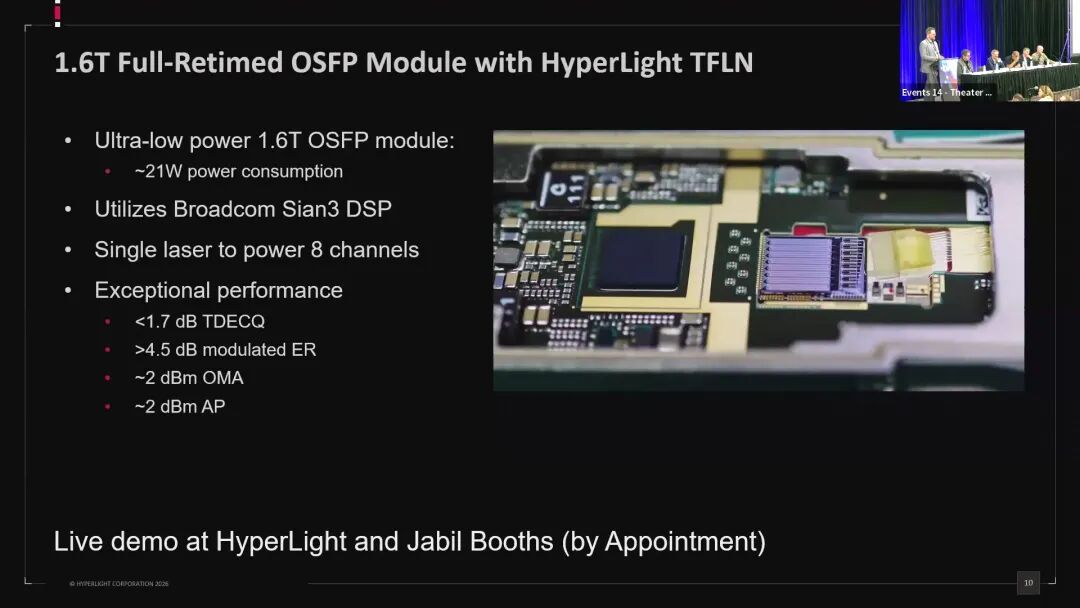

2. 数通领域:1.6T OSFP DR8 PIC已正式商用,分为两个版本:全重定时版本搭配Broadcom Siarn3 DSP,典型功耗约21W,室温运行功耗可低至20W;半重定时版本搭配Credo半重定时DSP,功耗低至12W。

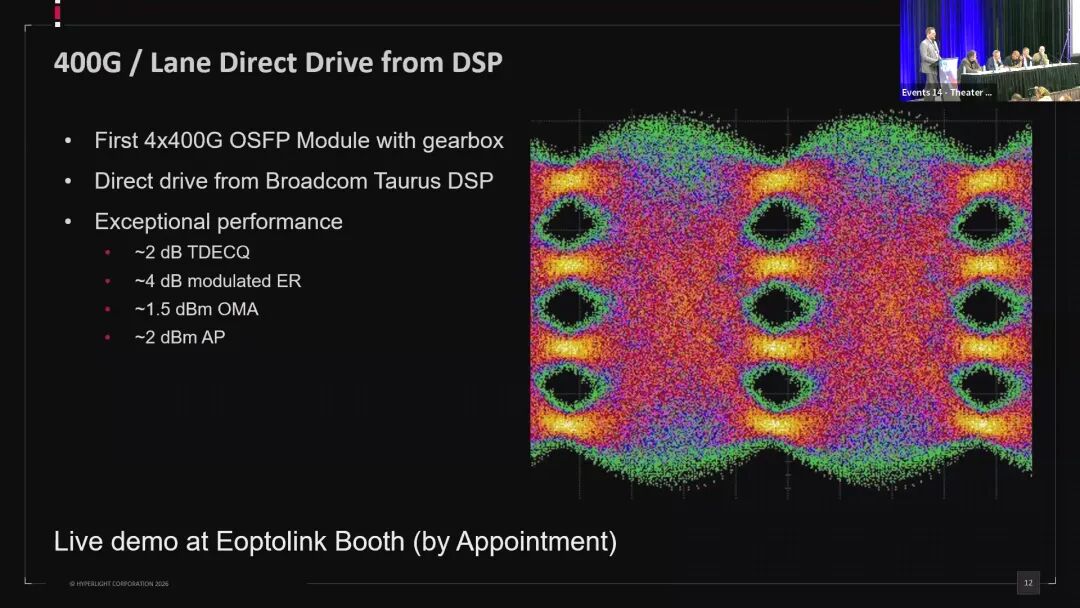

两款产品均实现单激光器驱动8通道,TFLN调制器可直接由低摆幅DSP输出驱动,Vπ<0.8V ppd,无需外置驱动器,实测性能达到>4.5dB调制消光比、<1.7dB TDECQ、~2dBm OMA。同时,400G/lane PIC已完成开发,搭配Broadcom Taurus DSP实现直驱,完成4x400G OSFP模块验证,实测~2dB TDECQ、~4dB调制消光比、~1.5dBm OMA,相关产品在OFC 2026完成现场实时演示。

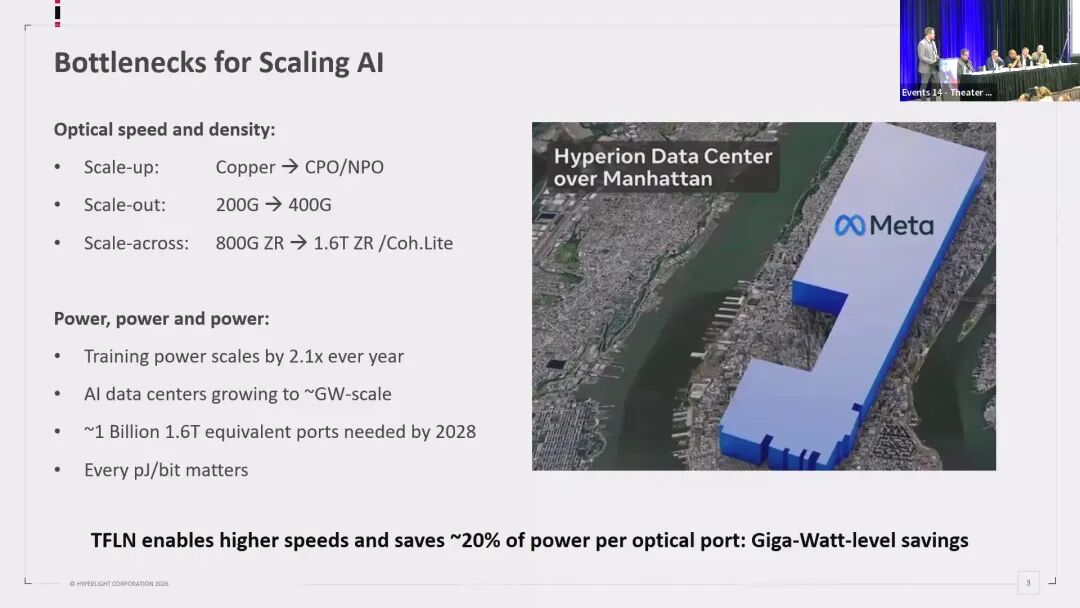

HyperLight TFLN方案可使单光口功耗降低约20%,可匹配AI数据中心GW级的功耗优化需求,同时其Chiplet平台支持2.5D/3D集成,可适配未来NPO/CPO架构的技术演进。

◆ 产业链落地:基于HyperLight TFLN的产品与制造验证

① Eoptolink:基于HyperLight TFLN的400G/lane产品标杆验证

Eoptolink是行业内最早布局TFLN商用的模块厂商之一,2022年OFC便发布了全球首个基于TFLN的800G DR8光模块,其核心产品均基于HyperLight TFLN器件开发,并配套Broadcom DSP完成系统级验证。

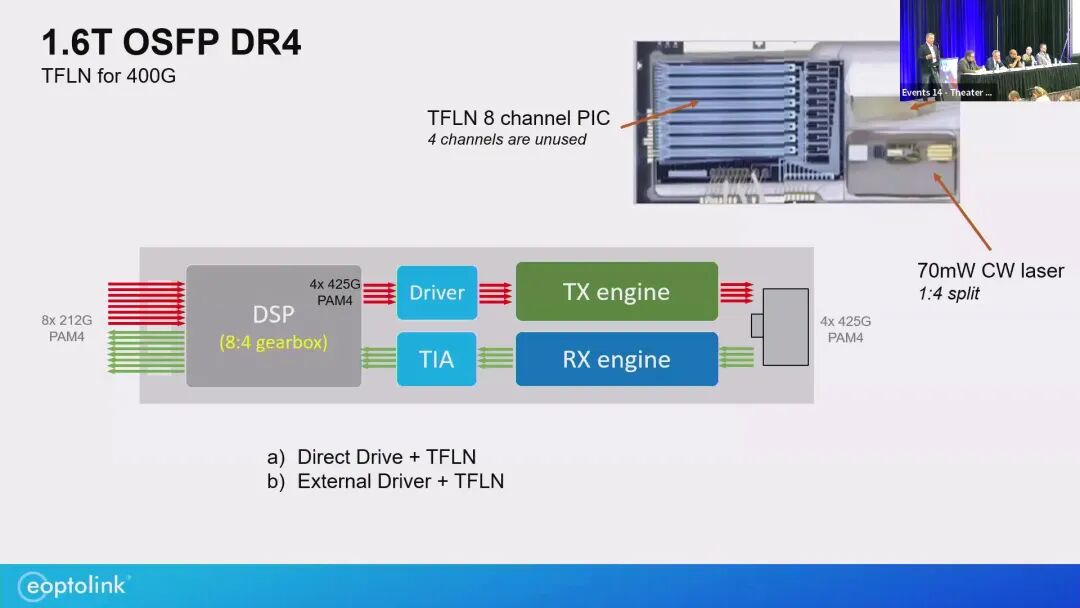

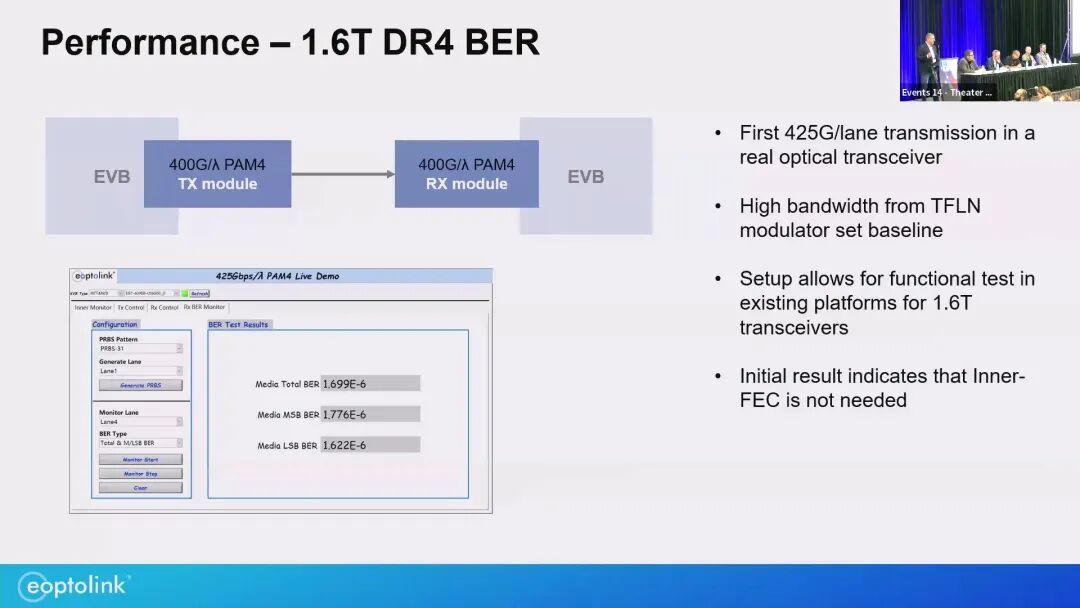

公司聚焦TFLN低驱动电压、低波导插入损耗的核心优势,开发了基于Broadcom Taurus DSP的1.6T OSFP DR4模块,内置8通道HyperLight TFLN PIC,完成了外置驱动与DSP直驱两种方案的对比验证:

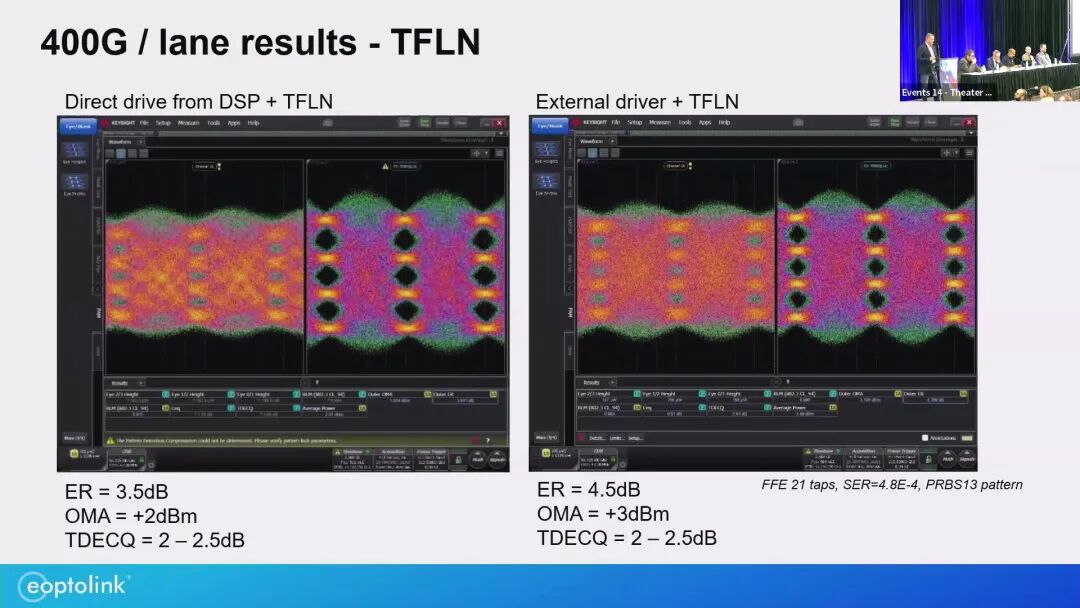

- DSP直驱方案:实现3.5dB消光比、+2dBm OMA、2-2.5dB TDECQ;

- 外置驱动方案:实现4.5dB消光比、+3dBm OMA、2-2.5dB TDECQ。

在链路层面,Eoptolink完成了425Gbps/lane PAM4实时传输演示,实测链路总BER达1.699E-6,达到200G/lane技术商用初期的同等性能水平,同时初步验证400G/lane场景无需内码FEC(InnerFEC)即可满足链路要求,为行业树立了400G/lane IMDD应用的性能基准。公司明确,TFLN技术已完全就绪400G/lane IMDD应用,将成为光模块从200G/lane向400G/lane演进的核心技术方案。

② Jabil:基于HyperLight TFLN的规模化制造能力建设

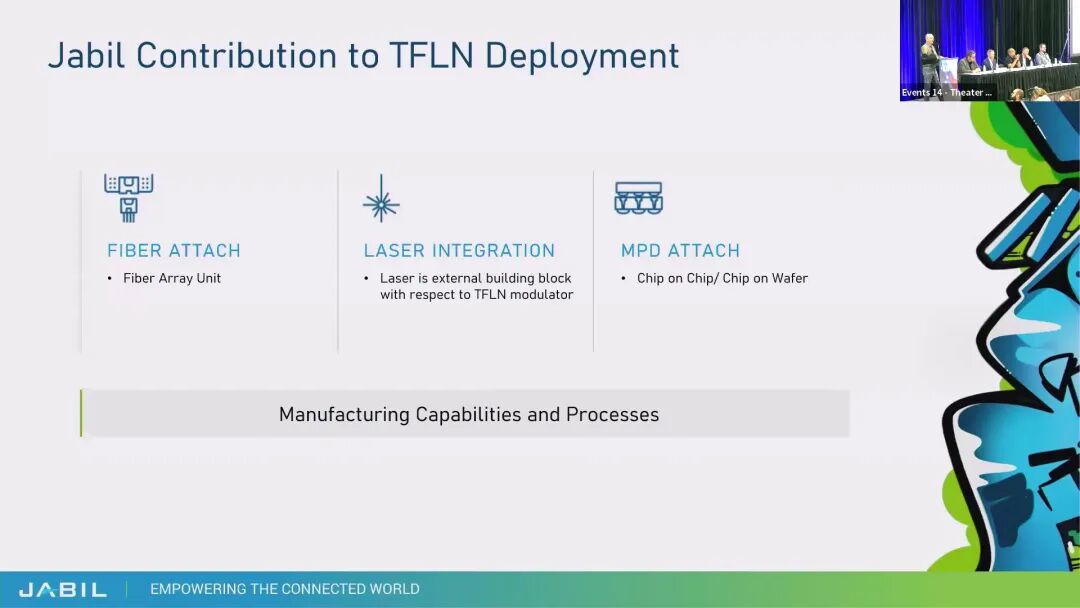

Jabil作为全球领先的光电子制造服务商,核心解决TFLN从芯片到规模化量产的制造落地问题,已完成与HyperLight TFLN器件的全流程制造工艺适配,是HyperLight核心的量产合作伙伴。

Jabil验证表明,TFLN制造工艺与现有硅光、磷化铟的成熟量产产线高度兼容,无需对设备、人力进行大规模改造,仅需对工艺方法进行针对性优化,即可实现规模化生产。目前公司已完成光纤阵列耦合、激光器集成、MPD贴片、芯片倒装/键合等全流程工艺开发,可完全适配TFLN PIC,支撑200G/400G per lane光模块、NPO光引擎的量产需求。

在OFC 2026,Jabil联合HyperLight完成了1.6T半重定时OSFP模块的现场演示,模块功耗低至12W,验证了量产工艺的稳定性与性能一致性。Jabil明确,TFLN已完成工业化验证,具备规模化量产的制造基础,应作为数据中心光子学生态的核心材料体系进行规模化导入。

◆ 行业头部厂商的技术视角与应用规划

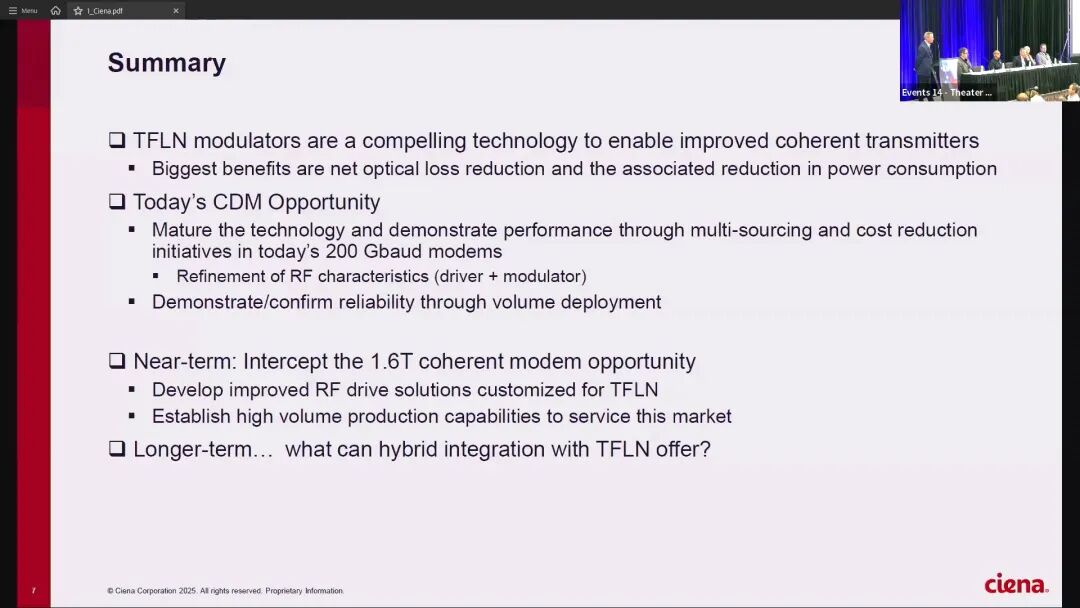

① Ciena:TFLN在相干光通信领域的全周期商用路径

Ciena作为全球长距相干光通信的头部厂商,从系统级应用的角度,完整论证了TFLN在相干传输领域的核心价值、已验证性能、商用路径与未来路线图。

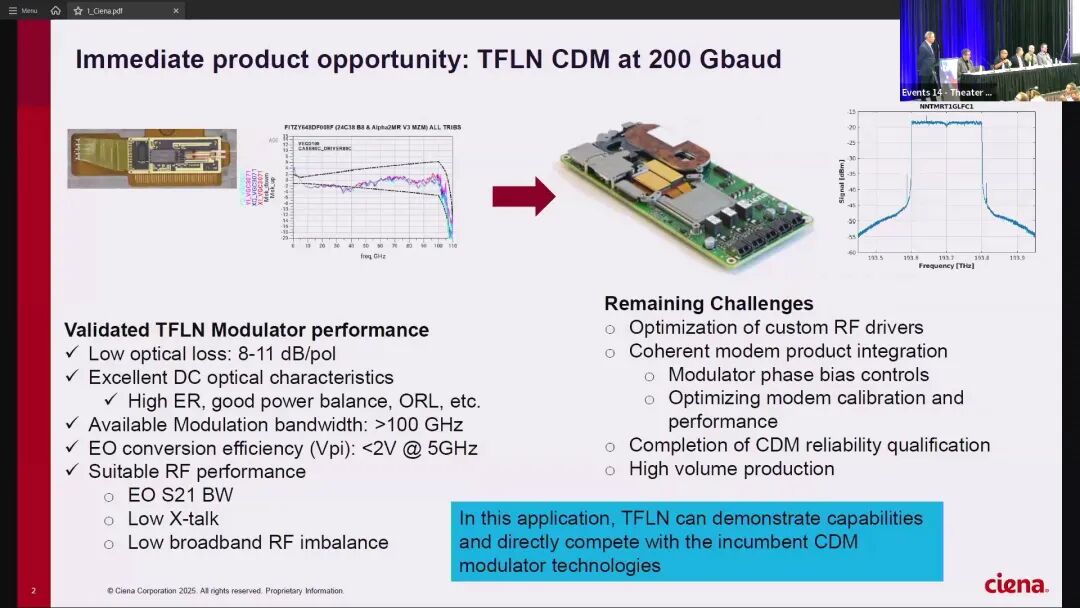

Ciena明确,TFLN的首个规模化商用场景,是当前已量产的200Gbaud相干驱动调制器(CDM)市场。CDM是相干传输的核心模块,已形成行业伪标准,TFLN调制器可直接与现有主流技术对标竞争,实现替代。

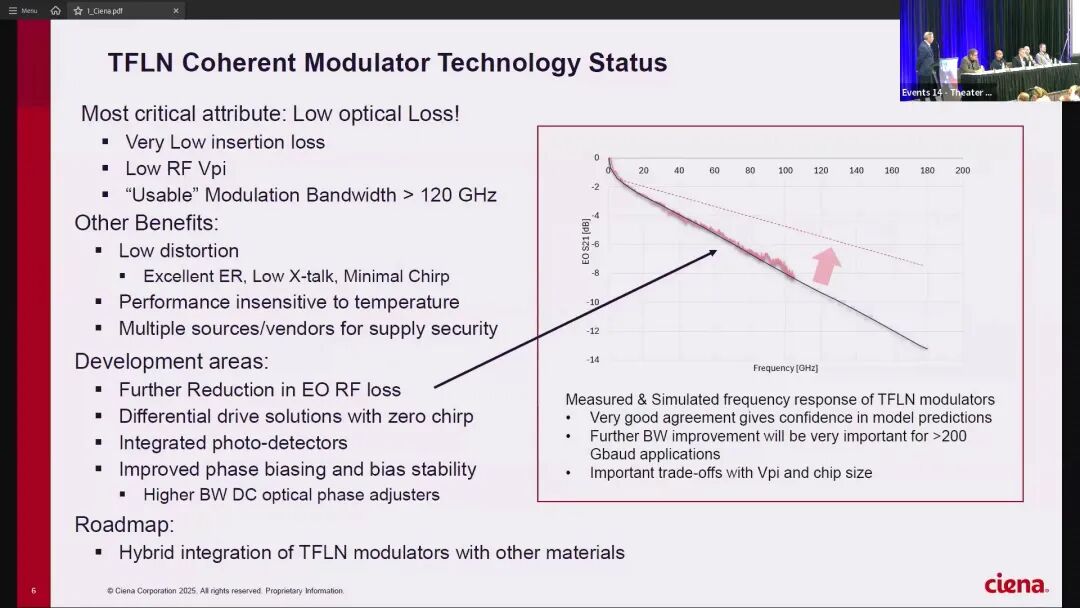

目前Ciena实验室已完成TFLN CDM的全项性能验证,核心指标如下:

- 电光转换效率:Vpi<2V@5GHz;

- 可用调制带宽:>100GHz;

- 光学特性:光插入损耗8-11dB/偏振,高消光比(ER)、优异的功率平衡与光回波损耗(ORL)、低串扰、低啁啾;

- 射频性能:低宽带射频失衡,适配相干系统的驱动需求。

核心技术价值:低插损是相干系统的核心命门

Ciena重点拆解了TFLN低插入损耗对相干系统的决定性意义,这也是其相较于现有技术的核心优势:

1. 1.6T及以上相干系统的OSNR瓶颈

现有相干发射机链路中,调制器典型插入损耗高达26dB,直接限制了光放大器的输入功率,进而决定了发射机的OSNR水平。以800G相干系统为例,+13dBm输入激光经过26dB调制器插损后,仅剩余-13dBm输入光放大器,最终Tx OSNR约38dB,对应ASE SNR仅28dB,已成为链路的核心噪声瓶颈。

当速率升级至1.6T时,符号速率翻倍,OSNR天然下降3dB,若要维持链路预算,必须将调制器插损降低3dB。而现有技术在带宽翻倍的同时,往往会出现RF损耗上升、Vpi升高的问题,无法实现插损优化,TFLN则可同时满足高带宽、低Vpi、低插损的三重需求。

2. 插损与系统功耗的强关联

调制器插损越高,所需的RF驱动电平、激光器输出功率就越高,甚至需要额外增加光放大器,直接推高全链路的功耗。对于超大规模AI数据中心,单端口每1W的功耗节省,在规模部署后可转化为MW级的总功耗优化。TFLN的低插损特性,可从根源上降低相干系统的功耗预算。

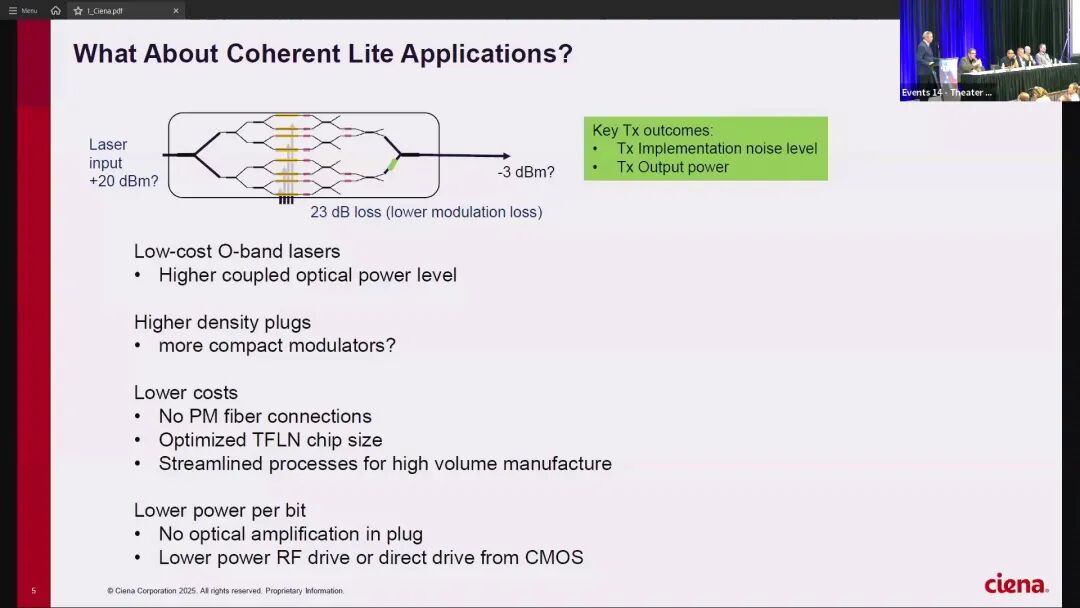

3. Coherent Lite短距场景的独特优势

针对3.2T Coherent Lite短距应用,行业核心需求是低成本、低功耗、无光放设计,通常采用O-band DFB激光器。TFLN在此场景具备两大核心优势:一是无高功率非线性吸收的瓶颈,可支持高输入光功率,最大化链路预算;二是低驱动电压可实现CMOS DSP直驱,无需外置RF驱动器,大幅降低功耗与成本。

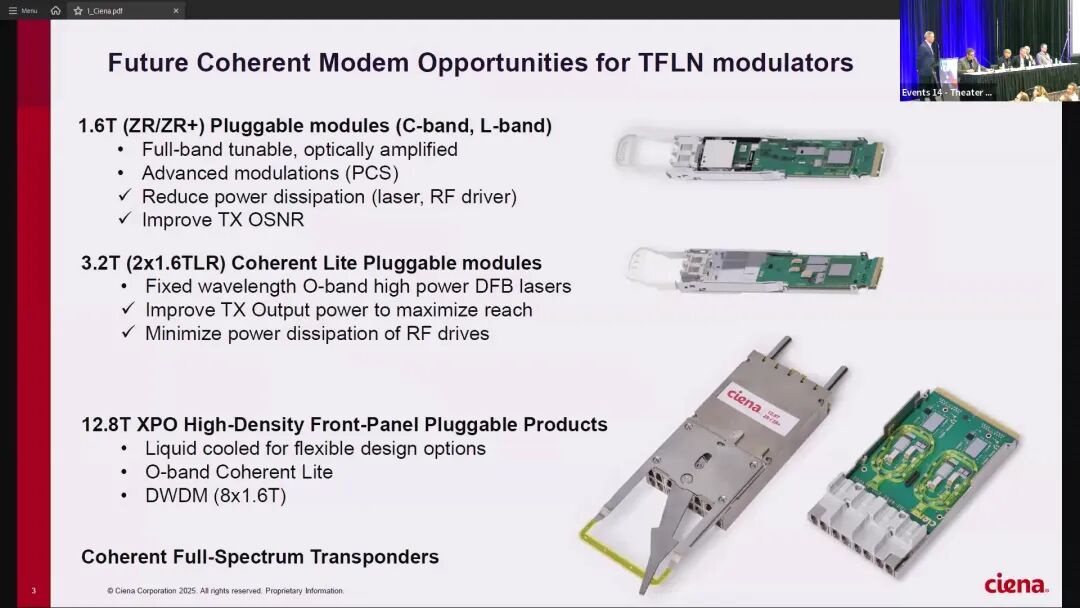

全周期商用路线图

Ciena制定了TFLN在相干领域的三步商用规划,覆盖从近期到长期的全场景需求:

1. 近期(1-2年):锁定1.6T ZR/ZR+可插拔模块市场,覆盖C/L波段全波段可调、光放大、PCS高阶调制场景,核心优化方向为定制化RF驱动方案、调制器相位偏置控制、相干调制器的可靠性认证与高量产能力建设;

2. 中期(2-3年):面向3.2T Coherent Lite可插拔模块市场,聚焦O-band短距应用,核心优化方向为TFLN芯片尺寸优化、高量产制造流程简化、低功耗RF驱动/CMOS直驱方案,最大化发射功率与链路预算;

3. 长期(3年以上):面向12.8T XPO高密度面板可插拔产品,适配液冷架构,支持8x1.6T DWDM全光谱转发器,核心依托TFLN的混合集成技术,实现超高速、高密度、低功耗的传输。

现存挑战与优化方向

Ciena同时明确了TFLN在相干应用中需要持续优化的方向:

- 射频驱动适配:现有TFLN调制器多为单端驱动,与行业主流的差分RF驱动器不匹配,存在功耗浪费问题,需加快差分驱动方案的开发与验证;

- 集成功能优化:需提升集成光电探测器的性能与保真度,优化热调谐相位调谐器的响应速度,提升相位偏置控制的稳定性与响应速度;

- 产业生态建设:需推动多源供应商体系建设,实现成本下降,同时完成全量可靠性认证与规模部署验证;

- 长期技术演进:推进TFLN与其他材料体系的混合集成,实现光放大、无源器件的单片/异质集成,进一步提升集成度与性能。

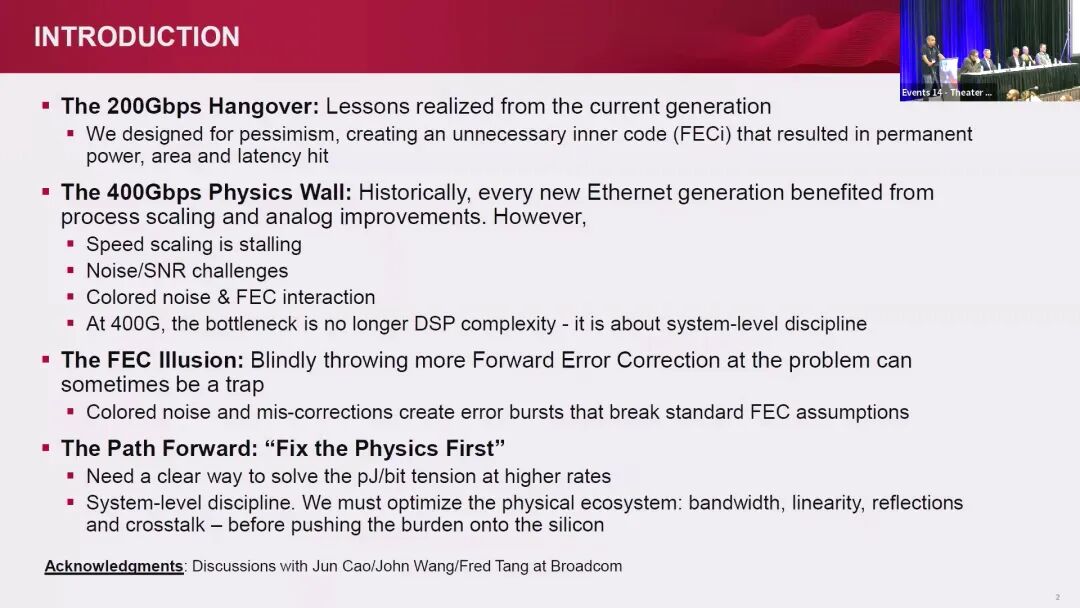

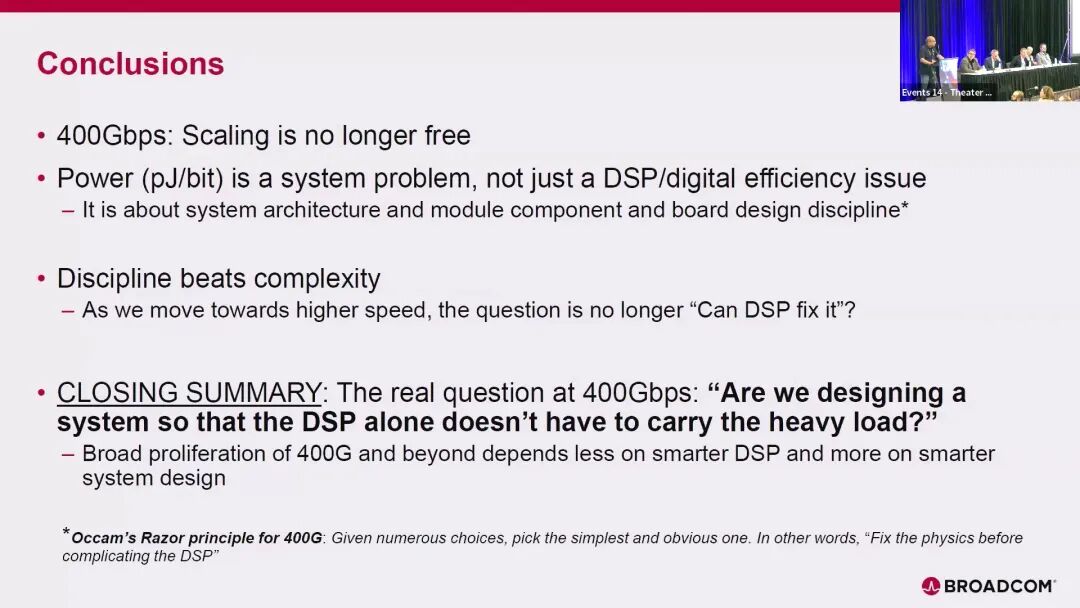

② Broadcom:400G/lane时代的系统级设计理念与TFLN的核心价值

Broadcom作为全球头部光通信DSP厂商,从系统级设计的底层逻辑出发,拆解了400G/lane时代的行业痛点,提出了“Fix the Physics First”的核心理念,并验证了TFLN在解决物理层瓶颈、降低系统功耗中的核心作用,

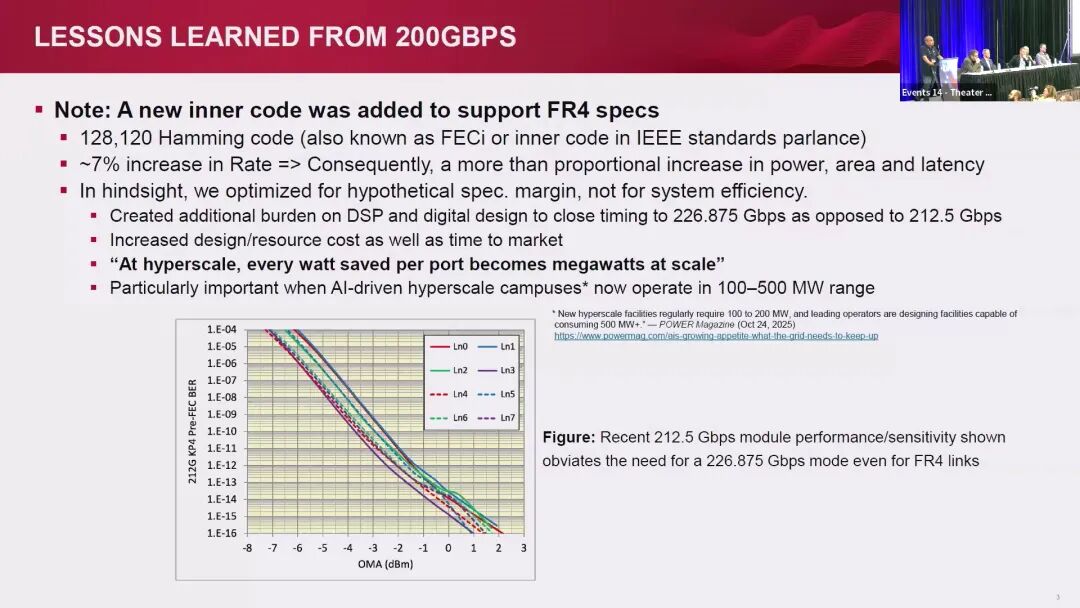

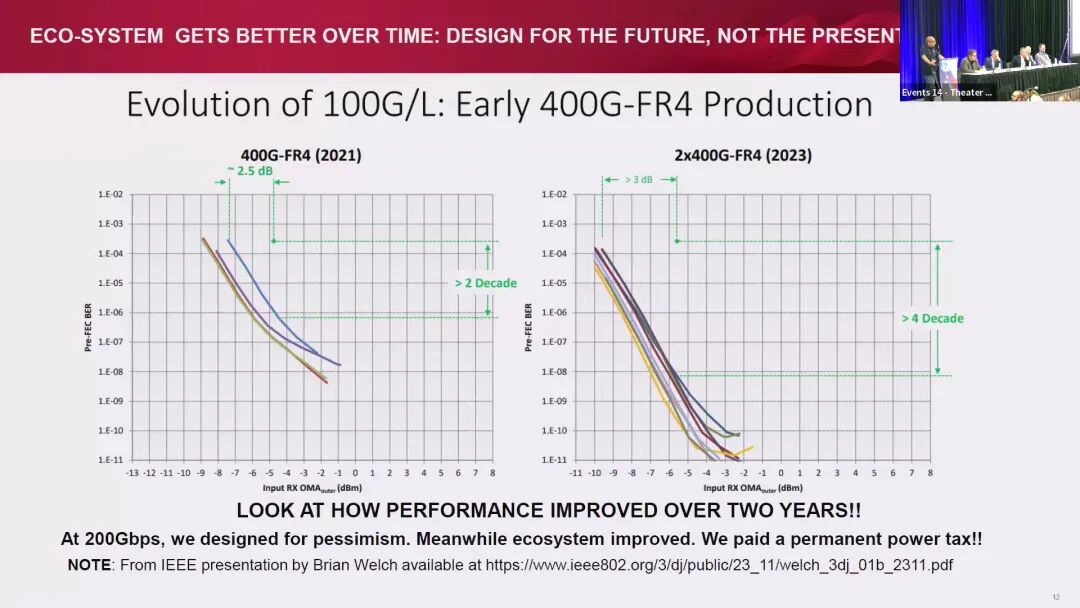

200G时代的核心教训:不必要的FEC带来的永久“功率税” Broadcom首先复盘了200G以太网标准化与商用过程中的核心教训,为400G时代的设计提供了关键参考:

200G标准化阶段,行业为悲观的链路场景假设,设计了128,120汉明内码(FECi),将单通道速率从212.5Gbps提升至226.875Gbps,带来了约7%的速率开销。该设计直接导致了永久性的功耗、芯片面积与时延提升,同时增加了DSP与数字设计的时序收敛难度,推高了设计成本与上市周期。 而后续的产业实践证明,随着板级设计优化、TIA/驱动带宽与线性度提升、电源IR Drop的严格控制、低抖动振荡器的普及,全链路生态得到了大幅改善,212.5Gbps模式已完全满足FR4链路的传输需求,之前设计的FECi完全不必要,行业为过度悲观的假设付出了长期的“功率税”。

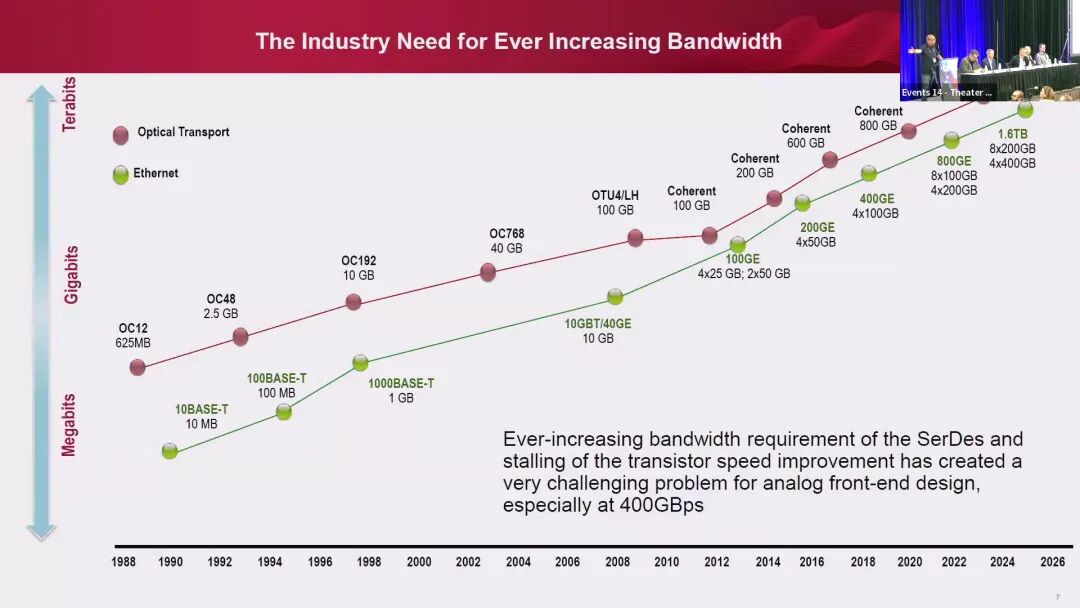

400G/lane时代的物理墙:缩放停滞与三大模拟瓶颈

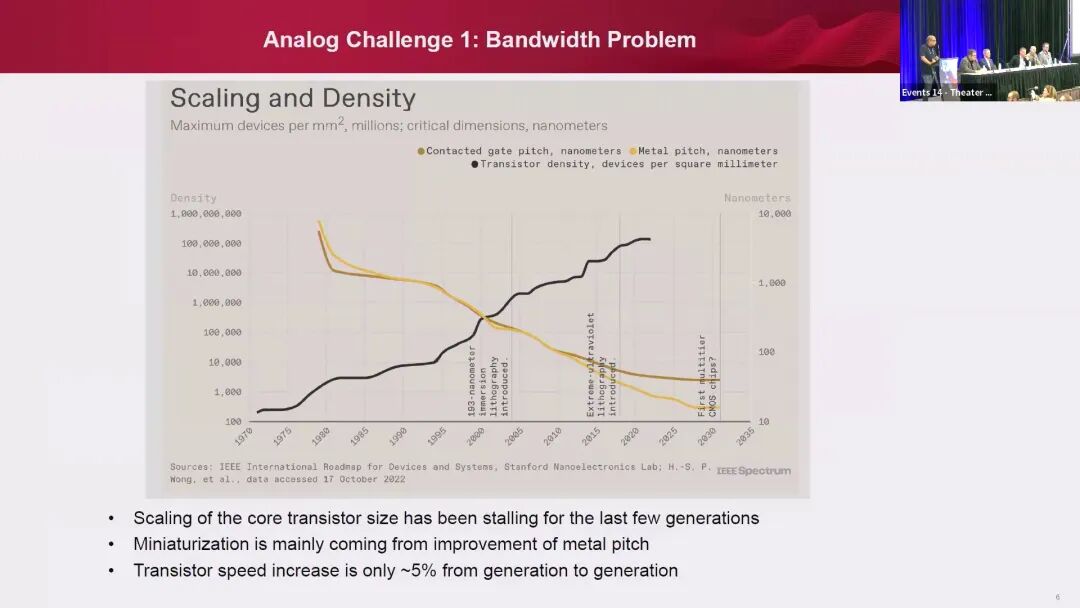

Broadcom明确,400G/lane时代,以太网速率缩放已不再“免费”,核心瓶颈已从DSP复杂度转向系统级物理层性能,晶体管缩放停滞带来的三大模拟瓶颈已无法通过DSP单独解决:

1. 晶体管缩放停滞:CMOS核心晶体管尺寸缩放已接近极限,每代工艺的晶体管速度提升仅约5%,完全无法匹配单通道速率从100G→200G→400G的翻倍需求,模拟前端的带宽提升已无底层器件支撑。

2. 三大核心模拟瓶颈

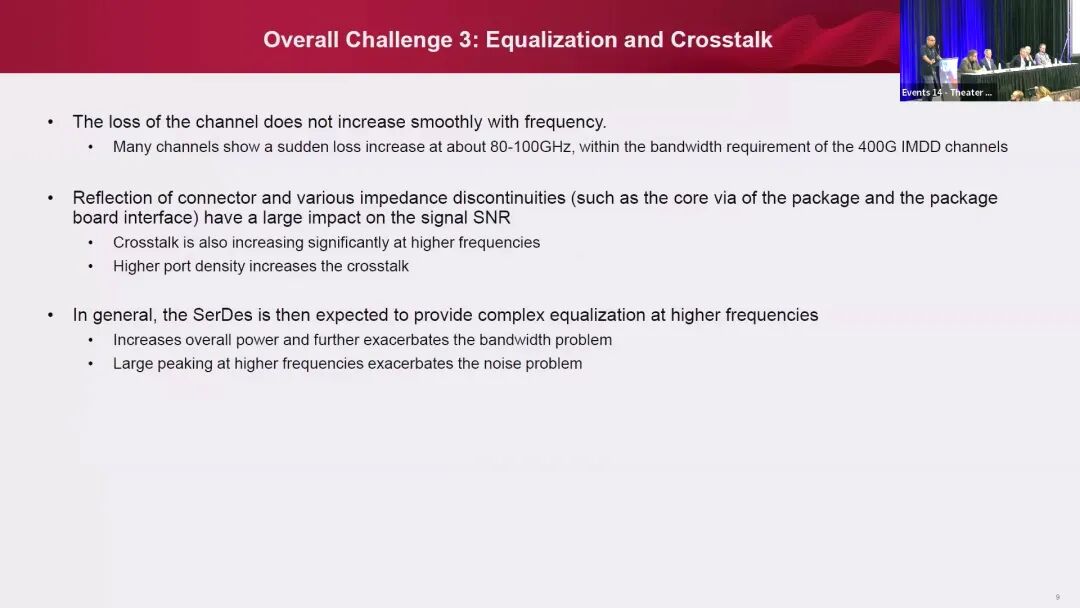

- 带宽瓶颈:400G/lane IMDD系统需要80-100GHz以上的通道带宽,而现有模拟前端、连接器、PCB通道的带宽无法满足,通道损耗在80-100GHz出现突变,严重恶化信号质量;

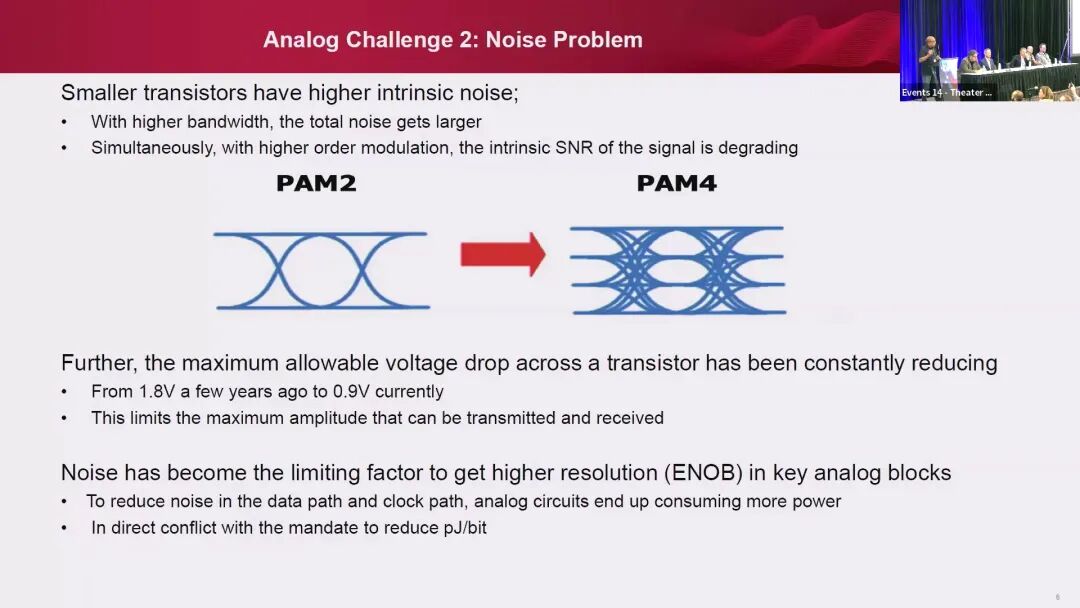

- 噪声瓶颈:更小尺寸的晶体管本征噪声更高,高带宽下总噪声进一步放大;同时PAM4等高阶调制对信号SNR要求更高,而晶体管供电电压已从早年的1.8V降至0.9V,限制了信号的最大发射摆幅,噪声已成为模拟性能的核心限制。为降低噪声,模拟电路需付出极高的功耗代价,与降低pJ/bit的核心目标直接冲突;

- 均衡与串扰瓶颈:连接器、封装过孔的阻抗不连续带来的信号反射,高密度端口带来的串扰,都会严重恶化信号SNR。若通过DSP的复杂均衡来补偿,不仅会带来极高的功耗开销,高频均衡的峰值放大还会进一步恶化噪声性能,形成恶性循环。

FEC的陷阱:理论增益无法落地的核心原因

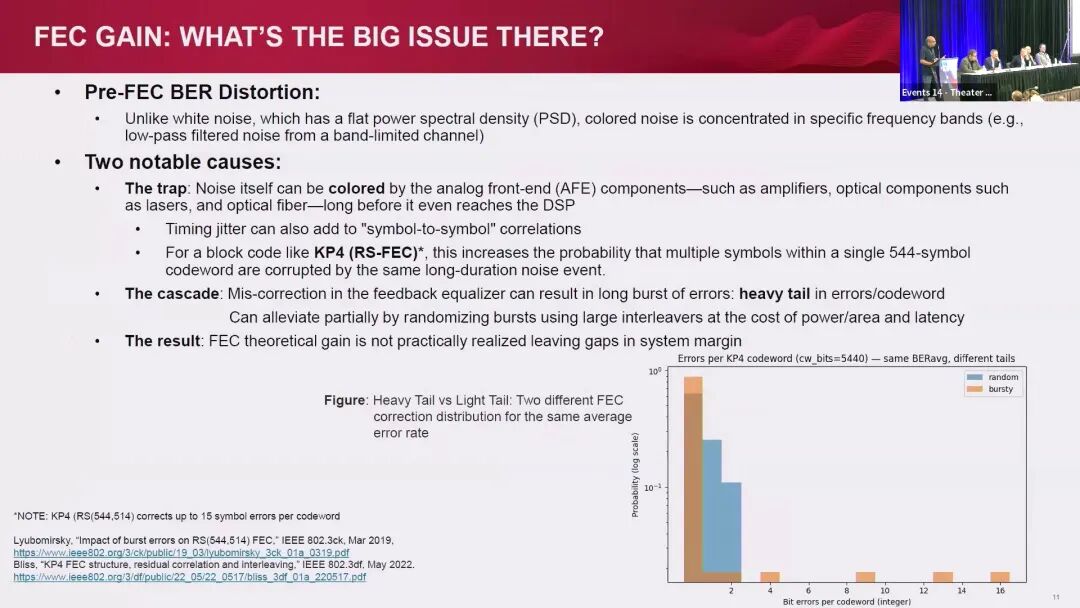

Broadcom重点指出了行业普遍存在的认知误区:盲目通过增加FEC开销、提升纠错能力来解决链路问题,往往是一个陷阱。

标准FEC的理论纠错增益,基于白噪声、随机误码的理想假设。但在实际的400G/lane链路中,有色噪声、信号反射、串扰会带来突发误码,形成误码分布的“重尾效应”,直接打破了标准FEC的设计假设,导致其理论纠错增益完全无法实现。盲目增加FEC开销,不仅无法解决链路问题,还会带来额外的功耗、时延、芯片面积开销,形成恶性循环。

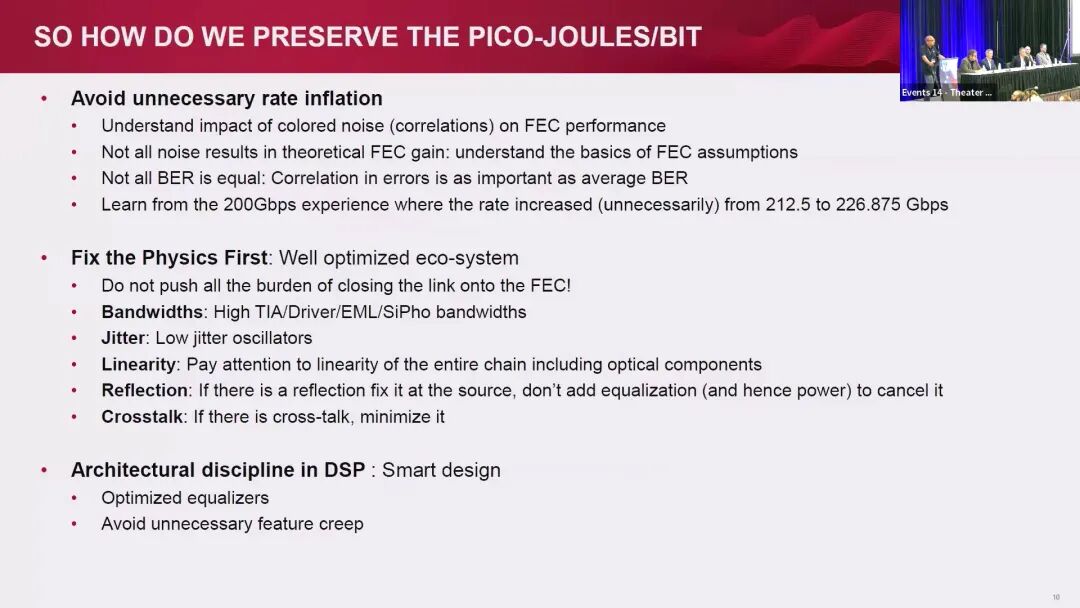

核心理念:Fix the Physics First(先修复物理层)

基于上述教训与痛点,Broadcom提出了400G/lane时代的核心设计原则——Fix the Physics First,并强调“纪律胜过复杂度”,遵循奥卡姆剃刀原则,优先选择最简单的解决方案。

该原则的核心逻辑是:必须先优化全链路的物理层性能,从根源上解决带宽、噪声、反射、串扰问题,而非将所有链路负担推给DSP与FEC。具体优化方向包括:

- 提升TIA、驱动器、光电器件的带宽与线性度;

- 采用低抖动振荡器,严格控制时序抖动;

- 从源头消除阻抗不连续带来的信号反射,而非通过均衡补偿;

- 从源头抑制串扰,而非通过DSP算法抵消;

- 保持DSP架构的设计规范,避免不必要的功能膨胀与复杂度提升。

TFLN的核心价值:从根源解决物理层瓶颈

Broadcom明确,TFLN是践行“Fix the Physics First”理念的核心器件方案,其超宽带宽、低驱动电压、低插入损耗的特性,可从物理层根源上解决400G/lane时代的核心瓶颈:

- 超宽带宽可满足400G/lane及以上的传输需求,无需复杂的高频均衡,大幅降低DSP的功耗开销;

- 低驱动电压可实现DSP直驱,无需外置RF驱动器,大幅降低发射机功耗与复杂度;

- 低插入损耗可提升发射机的光输出功率与SNR,降低链路预算压力,减少对强FEC的依赖。

目前,Broadcom已完成Taurus DSP与HyperLight TFLN调制器的400G/lane直驱方案的全链路闭环验证,实现了优异的TDECQ、消光比与BER性能,验证了该方案的可行性与性能优势。

◆ 论坛核心共识

本次论坛形成了TFLN产业发展的四大核心共识:

1. 技术拐点已至:TFLN已完成从实验室研发到商用产品的全流程验证,在200G/lane规模商用、400G/lane样机演示中均展现出显著的性能与功耗优势,可靠性、良率、量产能力均已达到工业化要求。

2. 核心价值明确:低插入损耗、低驱动电压、超宽带宽是TFLN的三大核心优势,可直接解决超高速相干与IMDD系统的功耗与OSNR瓶颈,完美适配AI数据中心与电信网络的超高速率、低功耗演进需求。

3. 产业链已闭环:以HyperLight等为的芯片厂商已实现TFLN芯片的规模量产与可靠性认证,Jabil等制造厂商完成了量产工艺适配,Eoptolink等模块厂商完成了产品级验证,Broadcom等头部DSP厂商完成了直驱方案的适配,全产业链生态已完全打通。

4. 核心挑战清晰:当前TFLN产业最大的挑战并非技术与量产能力,而是行业客户的规模化导入与产品设计迭代,完成从现有技术体系向TFLN的切换,实现全行业的规模部署。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-25,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读