OFC 2026 PDP:免Driver的TFLN光DAC(oDAC)实现448 Gbps PAM4与1.2 Tbps 16-QAM Coherent-Lite传输(McGill大学/Hyperlig

OFC 2026 PDP:免Driver的TFLN光DAC(oDAC)实现448 Gbps PAM4与1.2 Tbps 16-QAM Coherent-Lite传输(McGill大学/Hyperlig

光芯

发布于 2026-04-03 08:52:12

发布于 2026-04-03 08:52:12

基于已公开的数据中心互连(DCI)功耗拆解数据,该架构通过剔除eDAC、Tx DSP与射频驱动三大高功耗模块,可使相干收发机总功耗降低约23%,IM/DD收发机总功耗降低约30%,为超大规模AI系统所需的高吞吐、低功耗、低时延DCI光模块提供了全新的技术路径。

1. 研究背景与核心目标

超大规模AI系统的快速发展,推动以太网技术路线加速迭代,对DCI光收发机提出了更高吞吐、更低功耗与更低时延的核心需求。当前下一代DCI系统的性能瓶颈,已逐步从光电器件本身转移至DAC/ADC的带宽限制,其中发射端的eDAC更是成为核心约束。

现有提升eDAC带宽的技术方案,多依赖基于外部复用器的频域交织技术,该方案不仅增加了系统复杂度与功耗,且无法在CMOS工艺中集成实现。与此同时,eDAC在光发射机中承担的三大核心功能——将DSP生成信号转换为多比特波形、对符号流重采样以设定波特率、将比特映射为PAM4/16-QAM等多电平格式,均存在架构简化的空间。

值得注意的是,先进CMOS ASIC中的逻辑门开关速度,已超过实用化eDAC的带宽上限,且可天然输出约0.7 V的电平信号。基于此,本研究提出核心技术思路:剔除发射端DSP与多比特eDAC,采用“逻辑门驱动”的发射机架构,通过oDAC方案将多路二进制逻辑门输出合成为多电平波形,在兼容CMOS工艺的前提下,实现更高的有效DAC带宽与传输吞吐,同时大幅降低系统功耗与时延。

本研究的核心目标,是验证无eDAC、无发射端相关DSP的oDAC发射机的传输性能,量化其功耗收益,完成IM/DD与简化相干两大主流DCI场景的工程化验证。

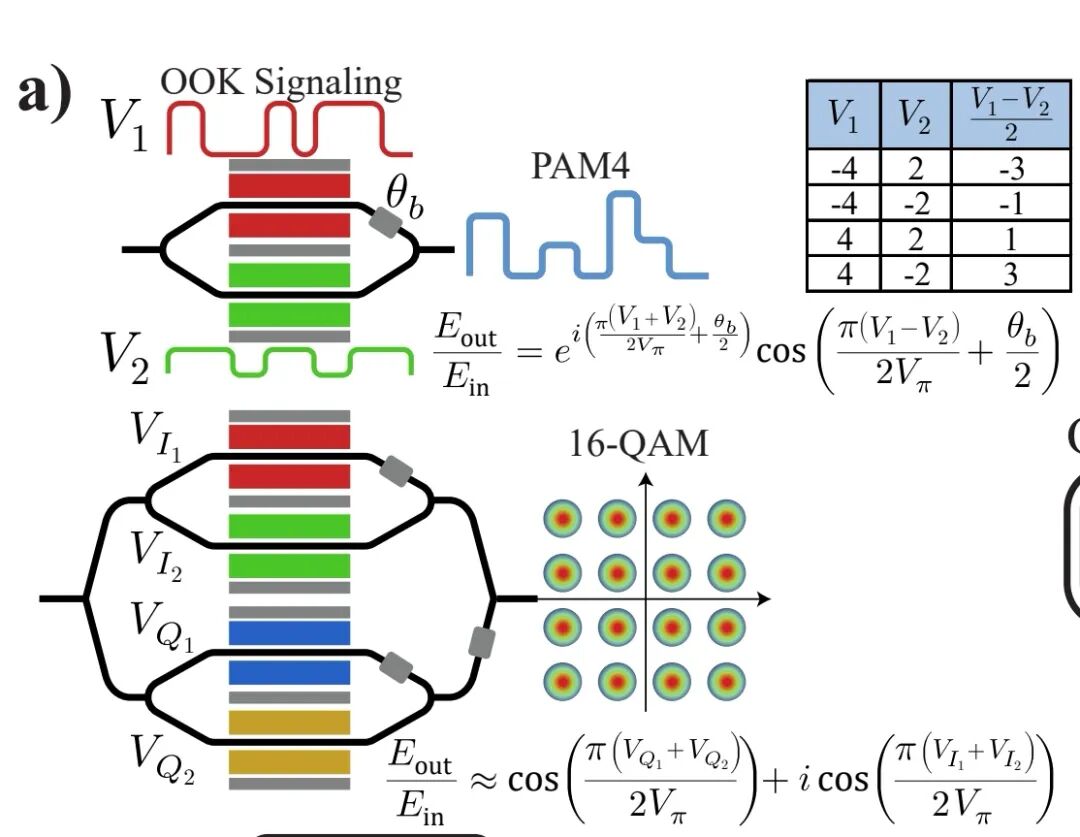

2. 基于薄膜铌酸锂(TFLN)的二进制加权光DAC核心架构

传统光DAC发射机多采用分段式马赫-曾德尔调制器(SE-MZM),每段对应1比特编码,通过段长设置实现二进制加权。但该方案存在三大固有缺陷:芯片占比随比特数同步缩放、无法降低驱动电压要求(有效VπL与推挽式MZM相当)、需对不同分段间的电延迟进行精密调谐,系统复杂度高。

本研究提出基于TFLN平台的并行二进制加权MZM(BW-MZM)oDAC架构,其核心设计与技术优势如下:

1. 双臂独立驱动架构:MZM的两个干涉臂由不同的差分逻辑电平信号独立驱动,通过双臂驱动将二进制通道合成为多电平输出,天然兼容CMOS逻辑门的直接驱动电压,无需额外射频驱动芯片。

2. 低VπL设计:BW-MZM为每个波导配置了本地差分电极对(S⁺/S⁻),可缩小波导周围的电极间隙,提升射频场强与波导的模式重叠度,相比传统GSSG推挽结构,显著降低了本征VπL乘积;结合双臂驱动带来的相位贡献,进一步放宽了驱动电压要求,为无驱动工作提供了核心支撑。

3. 差分驱动兼容性:该架构可直接兼容TFLN平台的差分驱动,解决了TFLN晶轴取向控制受限带来的差分信号电极布局难题。

4. 低复杂度布局:二进制输入可在光子集成芯片(PIC)上实现物理共址与对齐,彻底消除了SE-MZM方案所需的分段间精密电延迟调谐需求。

针对不同应用场景,该架构衍生出两大核心形态:

- IM/DD场景用BW-MZM:输出光场的幅度由(V₁-V₂)/2决定,通过设置V₁=2V₂的二进制加权驱动,可利用两路二进制信号生成四电平幅度,实现PAM4调制;通过调整加权方式,可兼容PAM6、PAM8等更高阶调制格式。该结构存在与(V₁+V₂)/2成正比的残余相位项,会引入啁啾,因此本研究选择在O波段1310 nm波长(标准SMF零色散波长附近)工作,最大限度抑制啁啾对传输的影响,适配DR8-2类传输距离需求。

- 简化相干场景用BW-IQM:在标准IQM偏置条件下,双臂共有的相位项不会在输出端转化为残余强度啁啾,可实现无啁啾的相干调制,适配长距离、高阶QAM调制的传输需求。

3. 实验测试方案设计

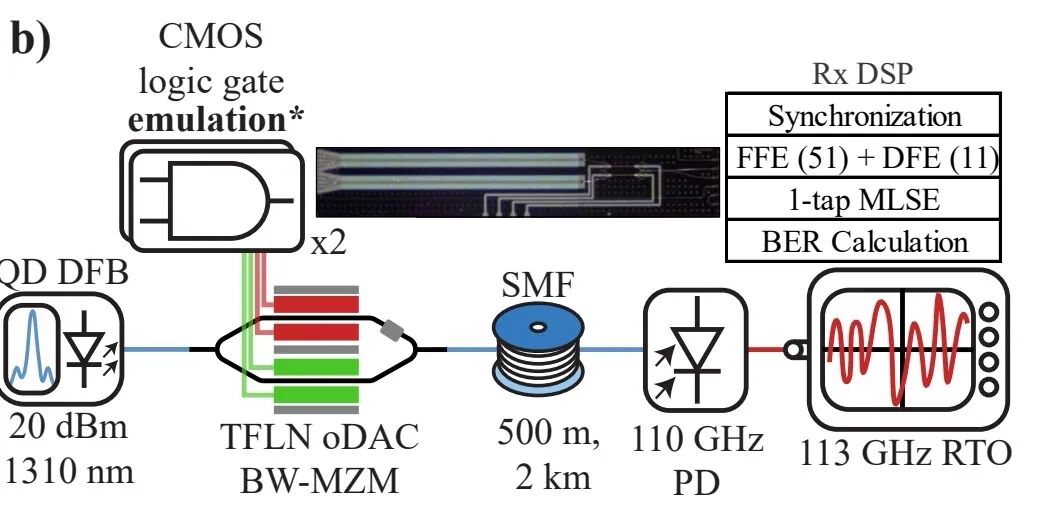

本研究分别搭建了IM/DD与简化相干两大实验平台,核心设计均围绕“无驱动、无Tx DSP、逻辑门直接驱动”的核心要求展开。

3.1 CMOS逻辑门输出仿真

为严格模拟CMOS逻辑门的输出特性,本研究采用3 nm CMOS工艺的7比特eDAC工作在1比特有效分辨率模式,彻底排除发射端DSP的使用可能,同时实现二进制加权的驱动信号输出:

- 最高有效位(MSB)信号V₁:7比特eDAC全部比特同时导通代表“1”,全部关断代表“0”;

- 最低有效位(LSB)信号V₂:仅使用eDAC的前6位LSB,严格满足V₁=2V₂的二进制加权条件,同时保留模拟逻辑门所需的1比特分辨率;

- 仿真逻辑门的核心参数:6 dB带宽110 GHz,差分输出电压600 mV,完全匹配先进CMOS逻辑门的电学特性。

3.2 IM/DD传输实验装置

1. 光发射链路:20 dBm输出的量子点(QD)DFB激光器提供1310 nm光载波,经仿真逻辑门输出的2路二进制信号直接驱动TFLN BW-MZM oDAC,完成PAM4/PAM6/PAM8信号的光域生成;该oDAC仿真6 dB带宽远超100 GHz,差分Vπ仅为2.2 V。

2. 传输链路:调制后的光信号经500 m或2 km标准单模光纤(SMF)传输。

3. 接收与信号处理:信号由110 GHz带宽光电二极管(PD)接收,经113 GHz实时示波器(RTO)采样后,完成信号同步、51抽头FFE+11抽头DFE、1抽头MLSE硬判决,最终完成误码率(BER)计算。

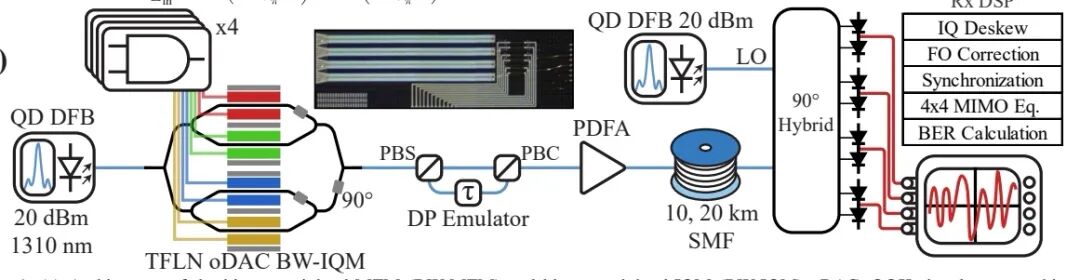

3.3 简化相干传输实验装置

1. 光发射链路:采用BW-IQM oDAC,由4路仿真逻辑门输出直接驱动,完成16-QAM/32-QAM/64-QAM信号的光域生成;光载波与IM/DD实验采用同一台20 dBm 1310 nm QD DFB激光器。

2. 传输链路:单偏振BW-IQM输出信号经双偏振(DP)仿真器生成DP-QAM信号,经掺镨光纤放大器(PDFA)放大后,通过500 m、10 km或20 km SMF传输。

3. 接收与信号处理:oDAC生成的DP-QAM信号与20 dBm 1310 nm QD DFB本振光一同输入2×8光混频器,经4路70 GHz平衡PD完成光电转换,由113 GHz RTO采样;后续完成IQ信号去偏移、重采样至每符号2个采样点、载波与本振频偏校正,采用4×4实系数MIMO均衡器补偿线性失真、相位噪声与平衡PD的带宽限制,最终基于恢复的符号完成BER计算。

3.4 对照实验设计

为实现公平的性能对比,本研究设置了传统推挽式MZM/IQM方案作为对照组,实验组与对照组采用完全相同的BW-MZM/BW-IQM器件;对照组采用7比特eDAC驱动,推挽模式下双臂驱动满足v₁=-v₂,同时调整调制光功率与实验组一致,精准量化oDAC方案的实现代价。

4. 关键测试结果与性能分析

本研究完成了IM/DD与简化相干两大场景的全参数测试,核心结果均达到了当前oDAC技术的最高水平,且实现代价极低。

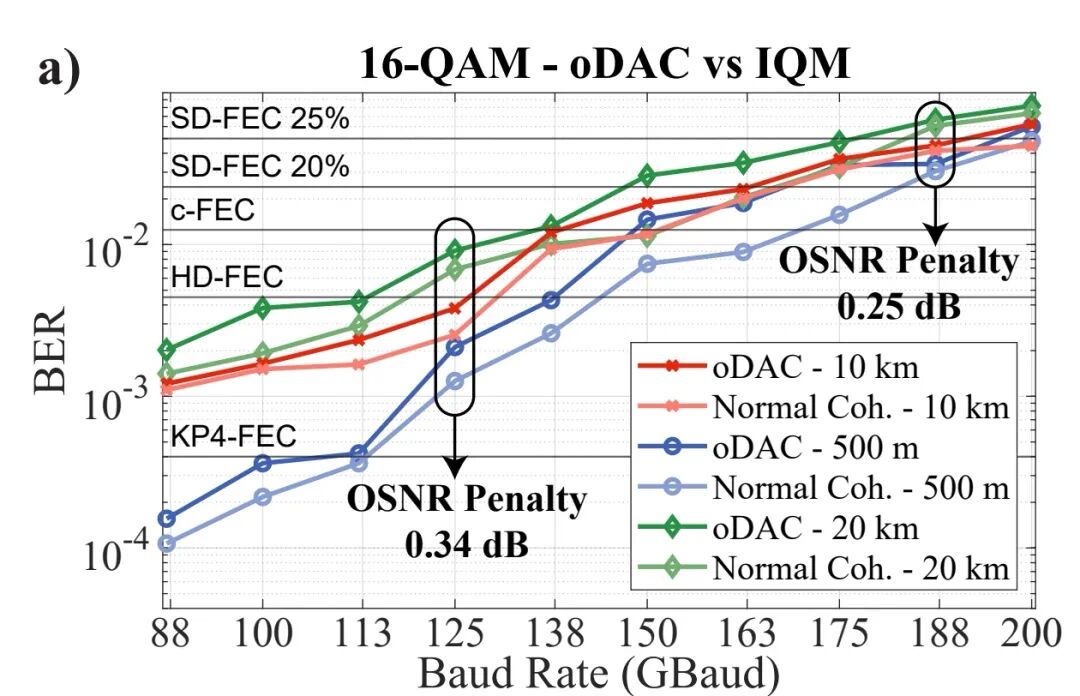

4.1 简化相干传输性能

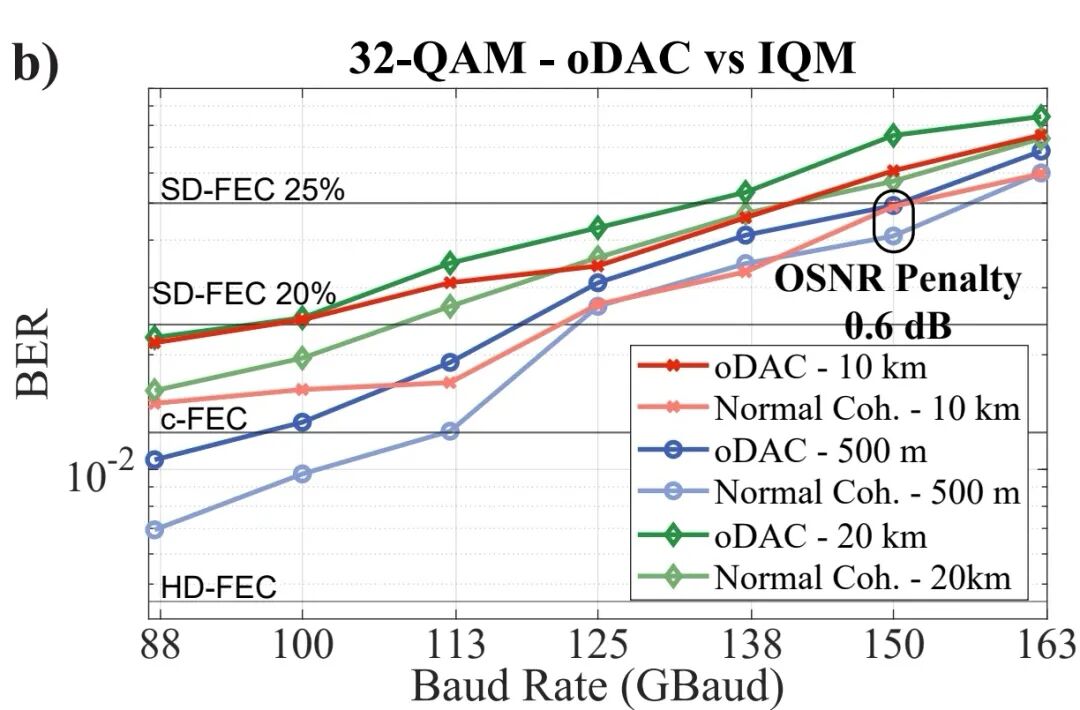

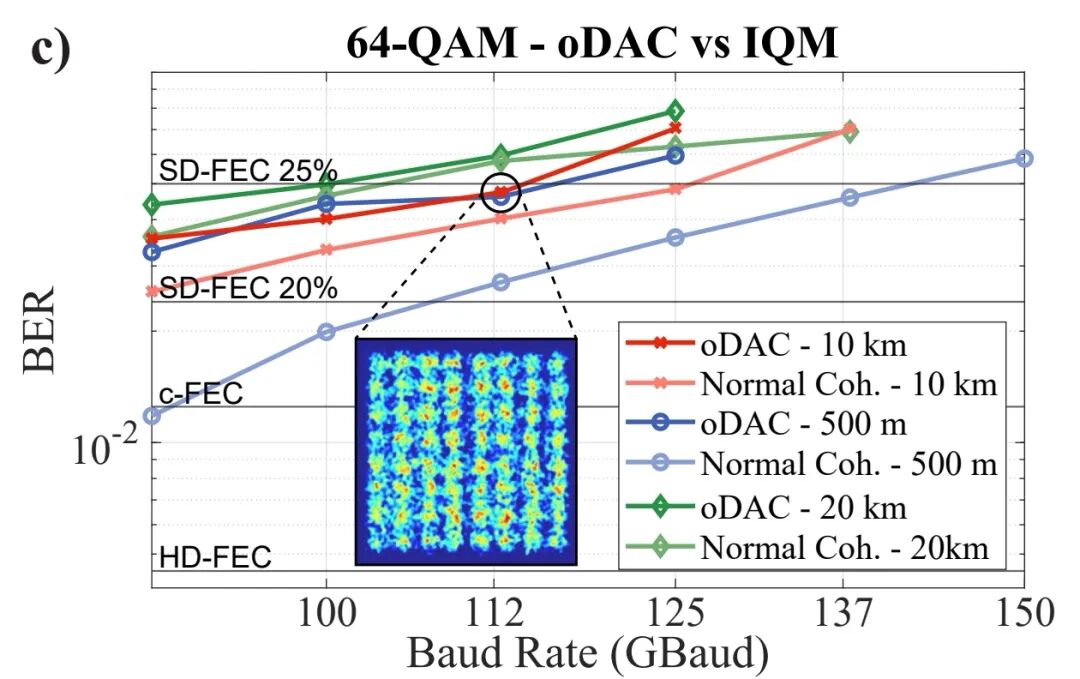

针对16-QAM、32-QAM、64-QAM三大高阶调制格式,完成了500 m、10 km、20 km距离的传输测试,核心结果如下:

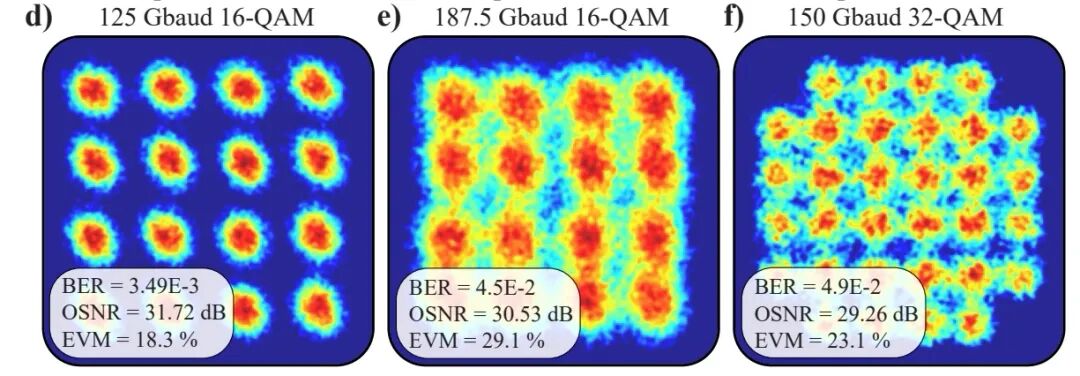

1. 16-QAM调制:在10 km传输距离下,实现了125 Gbaud DP-16-QAM信号的800 Gbps净速率传输,BER满足6.7%开销HD-FEC阈值;同时实现了187.5 Gbaud DP-16-QAM信号的1.2 Tbps净速率传输,BER满足25% SD-FEC阈值。与传统推挽式IQM方案相比,800 Gbps传输下OSNR代价仅0.34 dB,1.2 Tbps传输下OSNR代价进一步降至0.25 dB,性能与当前O波段相干800G-LR1标准的信令与BER指标对齐,同时实现了功耗的大幅降低。

2. 32-QAM调制:在500 m传输距离下,实现了150 Gbaud DP-32-QAM信号的1.2 Tbps净速率传输,BER满足25% SD-FEC阈值,与传统方案相比OSNR代价为0.6 dB。

3. 64-QAM调制:完成了500 m、10 km、20 km距离的传输验证,实测BER可匹配对应FEC阈值要求。

4. 测试结果显示,150 Gbaud以上的传输性能主要受限于平衡PD 70 GHz的带宽瓶颈,系统内其余器件带宽均超过100 GHz,后续通过升级接收端器件可进一步提升传输波特率与吞吐能力。

5. 实测星座图显示,DP-16-QAM与DP-32-QAM信号星座对称性优异,验证了该oDAC架构出色的传输线性度。

4.2 IM/DD传输性能

针对PAM4、PAM6、PAM8调制格式,完成了背靠背(B2B)、500 m、2 km距离的传输测试,核心结果如下:

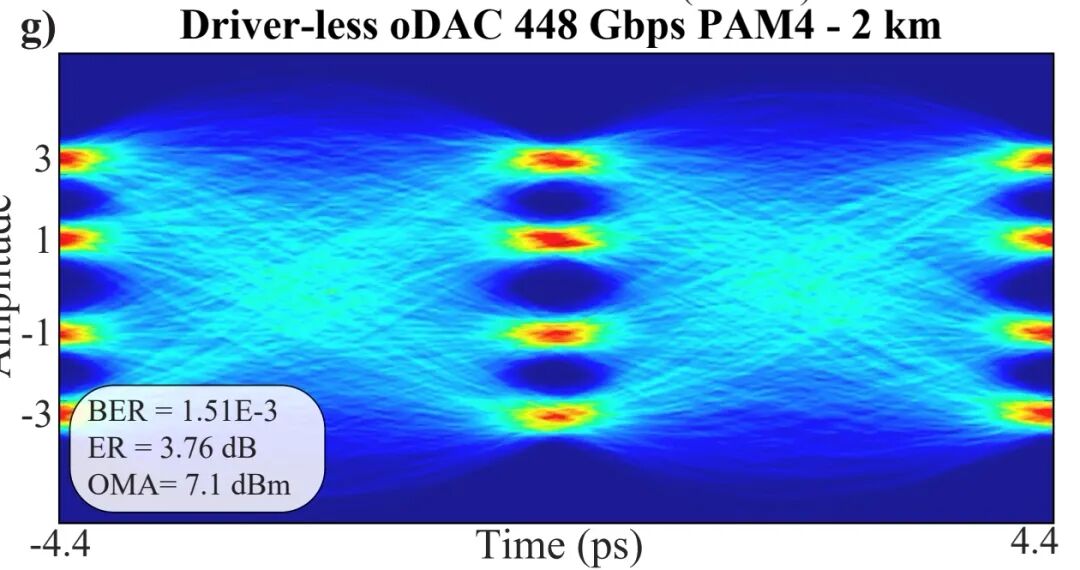

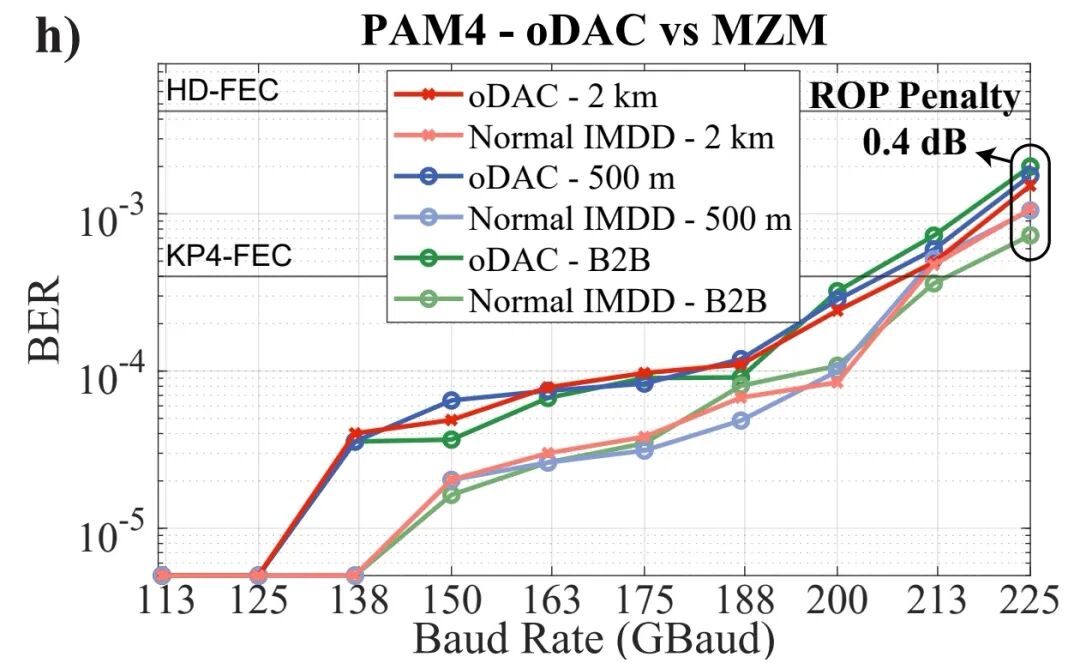

1. PAM4调制:在2 km传输距离下,实现了225 Gbaud PAM4信号传输,净速率达448 Gbps,BER远低于6.7%开销HD-FEC阈值;实测消光比(ER)达3.76 dB,超过200G IEEE标准的最低消光比要求。B2B与2 km传输性能无明显差异,验证了O波段工作下,啁啾对2 km距离内的传输无实测性能劣化,完全适配DR8-2类应用场景。与传统推挽式MZM方案相比,接收光功率(ROP)代价仅0.4 dB。

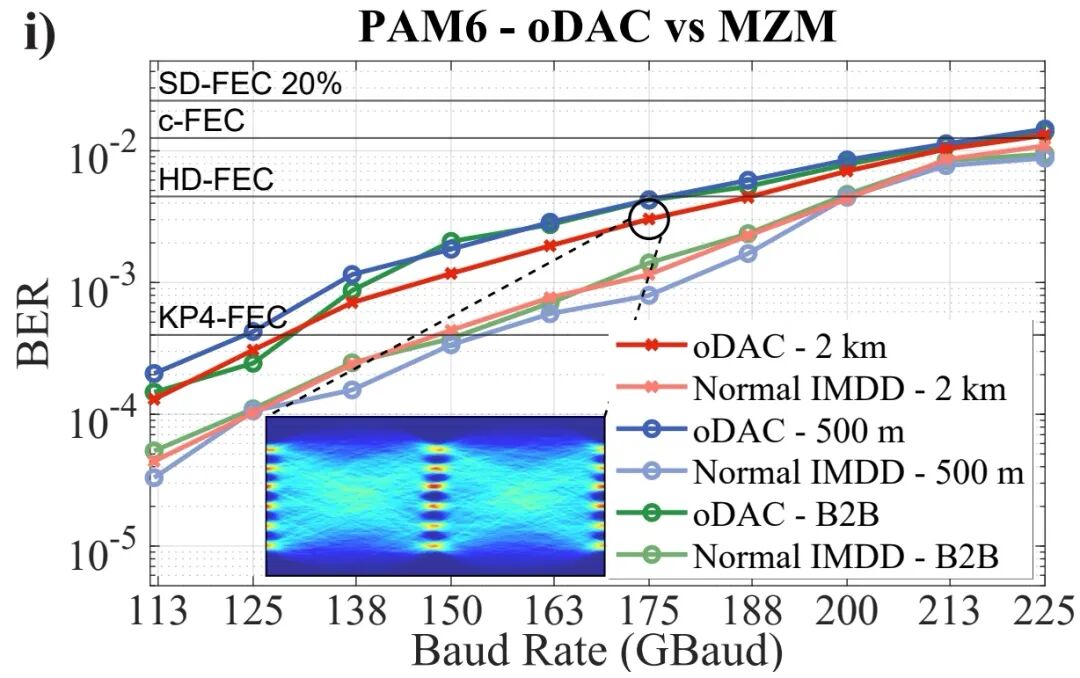

2. PAM6调制:B2B、500 m、2 km距离下性能表现一致,在2 km传输距离下,175 Gbaud PAM6信号实现了410 Gbps净速率传输,BER满足对应FEC阈值要求。

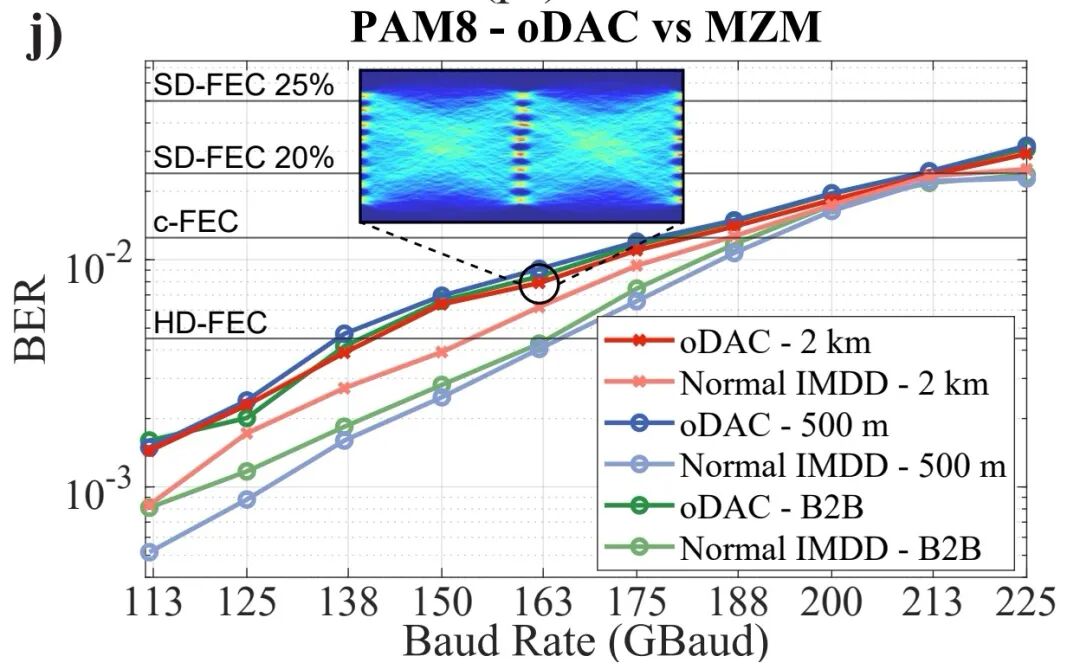

3. PAM8调制:不同传输距离下性能波动极小,162.5 Gbaud PAM8信号在c-FEC阈值下实现425 Gbps净速率传输,225 Gbaud PAM8信号在25% SD-FEC阈值下实现540 Gbps净速率传输。

上述结果验证了该oDAC架构可兼容4/6/8电平幅度调制,完全满足下一代DCI 400G单通道的符号率与调制格式需求。

4.3 功耗收益评估

基于已公开的DCI收发机功耗拆解数据,本研究提出的架构剔除了eDAC、Tx DSP、射频驱动三大发射端核心高功耗模块,在保守估算条件下,可使相干收发机的总功耗降低约23%,IM/DD收发机的总功耗降低约30%,为下一代高密DCI光模块的功耗优化提供了颠覆性的解决方案。

5. 研究结论

本研究首次实现了无驱动、CMOS逻辑门直接驱动的oDAC发射机,在无发射端DSP、无多比特eDAC的极简架构下,完成了IM/DD与简化相干两大场景的高速传输验证,实现了2 km距离下448 Gbps PAM4、10 km距离下1.2 Tbps DP-16-QAM的高性能传输,实测实现代价可忽略不计,同时带来了收发机功耗的量级优化。

该成果是业界首个无驱动oDAC工程化实现,创造了当前oDAC技术的最高传输速率纪录,为超大规模AI系统所需的高吞吐、低功耗、低时延DCI光互连技术提供了全新的技术范式

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-03-24,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读